Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:16.

- Laatst gewijzigd 2025-01-23 15:01.

In deze instructable gaan we een SPI Bus Master helemaal opnieuw ontwerpen in VHDL.

Stap 1: Overzicht van SPI

- SPI is een synchrone seriële bus

- Zijn populariteit en eenvoud maakten het een de facto standaard in seriële communicatie

- Full-duplex bus

- Eenvoudig protocol en een van de snelste seriële bus

Stap 2: Ontwerpspecificaties

Dit zijn de specificaties van de SPI Master die we gaan ontwerpen:

- Ondersteunt alle vier de werkingsmodi; dynamisch configureerbaar

- Klok inschakelen controle voor energiebesparing

- Statisch configureerbare woordlengte en snelheid

- Enkele onderbreking voor zowel verzending als ontvangst

Stap 3: Beginnen

Allereerst moet ons IP-adres twee interfaces hebben. De ene is een seriële interface en de andere is een parallelle interface. Seriële interface bestaat uit de de-facto standaardsignalen van SPI: MOSI, MISO, SS, SCLK.

MOSI wordt soms SDO genoemd en MISO wordt soms SDI genoemd.

Seriële interface wordt gebruikt om te communiceren met externe randapparatuur, bijv. SPI-slaves.

Parallelle interface wordt gebruikt om te communiceren met onze host, dat wil zeggen een microcontroller of microprocessor, die de Master daadwerkelijk vertelt welke gegevens serieel moeten worden verzonden en ontvangen via de seriële lijnen. dat wil zeggen, alle databussen behoren tot een parallelle interface.

We hebben een globale klok die de interne SPI-logica aanstuurt, evenals SCLK, die we intern genereren.

We hebben ook enkele stuursignalen, zoals schrijven inschakelen, klok inschakelen. En interrupt- en andere statussignalen.

Omdat we te maken hebben met complexe regelomstandigheden, is het eenvoudiger om dergelijke seriële communicatie-IP's als een FSM te ontwerpen. We zullen de SPI-master ook als FSM ontwerpen. De FSM wordt aangedreven door een andere interne klok die twee keer SCLK is. Die interne klok wordt gegenereerd met behulp van synchrone tellers van de globale klok.

Alle stuursignalen die klokdomeinen overschrijden, hebben synchronisatoren om aan de veilige kant te zijn.

Stap 4: RTL-weergave van de SPI Master Core en simulatiegolfvormen

Het is een kaal RTL-ontwerp zonder speciale FPGA-IP's. Daarom is het een volledig overdraagbare code voor elke FPGA.

Aanbevolen:

Ontwerp van zelfstudievideogames: 6 stappen

Ontwerp van videogames: ik ben een hobbyistische game-ontwikkelaar, met mijn grootste interesses in het ontwerpen en programmeren van games. Om mijn vaardigheden te oefenen en op te frissen, maak ik af en toe eenvoudige games die ik deel met mijn vrienden en broers en zussen. Eerder zou ik de regels uitleggen aan de pla

Ontwerp van UART in VHDL: 5 stappen

Ontwerp van UART in VHDL: UART staat voor Universal Asynchronous Receiver Transmitter. Het is het meest populaire en eenvoudigste seriële communicatieprotocol. In deze instructable leert u hoe u een UART-module in VHDL ontwerpt

Hoe voldoen de uitdagingen van het ontwerp van de voeding door DC-DC Technologies: 3 stappen

Hoe komen de uitdagingen van het ontwerp van de voeding samen door DC-DC Technologies: Ik zal analyseren hoe DC-DC Technologies de uitdaging van het ontwerp van de voeding aangaat. stroom. In draagbare apparaten, hogere efficiëntie ext

Voorlopig* SPI op de Pi: communiceren met een SPI 3-assige versnellingsmeter met behulp van een Raspberry Pi: 10 stappen

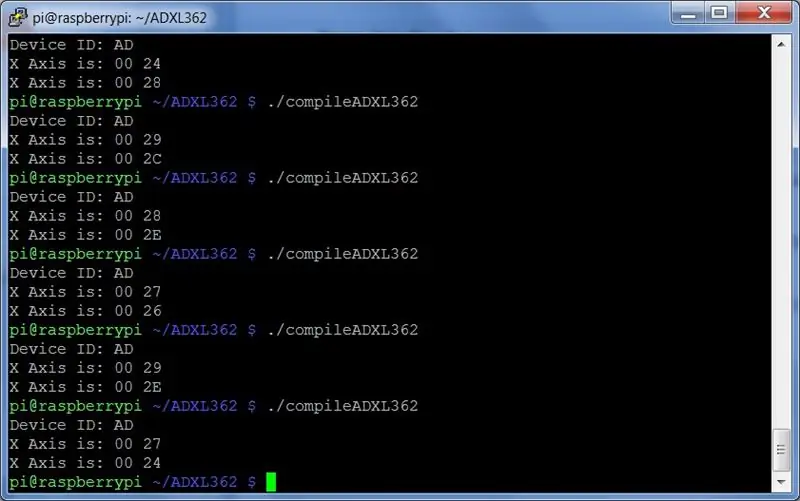

Voorlopig* SPI op de Pi: communiceren met een SPI 3-assige versnellingsmeter Een Raspberry Pi gebruiken: stapsgewijze handleiding voor het instellen van Raspbian en communiceren met een SPI-apparaat met behulp van de bcm2835 SPI-bibliotheek (NIET bit-banged!) Dit is nog steeds heel voorlopig… Ik moet betere foto's van de fysieke aansluiting toevoegen en een aantal lastige code doornemen

Instructies voor het voltooien van de mock-up van het ontwerp van de rupsschuif voor het heffen/verlagen van in het midden gemonteerde voetsteunen op elektrische rolstoelen - Ajarn

Instructies voor het voltooien van de mock-up van het ontwerp van de rupsschuif voor het omhoog/omlaag brengen van in het midden gemonteerde voetsteunen op elektrische rolstoelen: in het midden gemonteerde voetsteunen kunnen omhoog worden gebracht om onder de zitting goed te worden opgeborgen en omlaag om te worden ingezet. Een mechanisme voor onafhankelijke bediening van het opbergen en plaatsen van de voetsteun is niet inbegrepen in elektrische rolstoelen op de markt, en PWC-gebruikers hebben de behoefte geuit