Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:16.

- Laatst gewijzigd 2025-06-01 06:10.

In deze instructable wordt het ontwerpen van een eenvoudige I2C-master in VHDL besproken.

OPMERKING: klik op elke afbeelding om de volledige afbeelding te zien

Stap 1: I2C-busoverzicht

•Staat voor Inter Integrated Circuit.

•Synchroon, Half duplex.

•Tweedraadsinterface - SDA en SCL.

•SDA - Seriële datalijn bestuurd door Master en Slave

•SCL - Seriële klok gegenereerd door Master

•Multi-master, Multi-slave-protocol.

•Twee modi - 100 kbits/sec en 400 kbits/sec: langzaam en snel.

Stap 2: RTL-ontwerp in VHDL

Ontwerpspecificaties van onze I2C Master

- 8-bits dataframe.

- Alleen SCL unidirectionele bediening.

- 7-bits slave-adres.

- Ondersteunt zowel langzame als snelle modi.

- Enkele master, meerdere slaven.

- Voldoet aan de originele I2C-specificaties van Philips.

Er wordt gebruik gemaakt van pure RTL-code. Het IP-adres is dus gemakkelijk overdraagbaar over alle FPGA's. Compact FSM-gebaseerd ontwerp met intern gegenereerde klok zorgt voor optimale oppervlakte en prestaties.

Stap 3: Simulatie en testen

Test omgeving

- Functionele simulatie en testen met behulp van I2C Slave IP van derden.

- Gesynthetiseerd met behulp van Xilinx Vivado gereedschapsset.

- Geïmplementeerd en getest op Artix-7 FPGA bord.

- Timing geverifieerd ontwerp voor 100 MHz.

- Geteste golfvormen op DSO/CRO.

- Succesvol geteste communicatie met Arduino UNO als I2C Slave.

Stap 4: Belangrijke opmerkingen

- Configureer tijdens het testen van Master met I2C Slave IP de slave-code volgens uw vereisten. Misschien wilt u de standaardklokfrequentie en het slave-adres wijzigen. De klokfrequentie moet ook in de mastercode worden geconfigureerd.

- Vergeet tijdens het testen aan boord de pull-up-weerstanden niet, aangezien de SDA-lijn een gemeenschappelijke afvoeruitgang is !!! Controleer google voor de aanbevolen pull-up-weerstand voor verschillende i2c-snelheden. Ik gebruikte 2.2K voor 100 kHz.

- Als u geen testbank gebruikt en de Master onafhankelijk simuleert, simuleer dan zorgvuldig het SDA-signaal, aangezien het een bidirectioneel signaal (inout) signaal is. Het heeft twee drivers, masterzijde en slavezijde. U moet weten wanneer u moet 'dwingen' en wanneer u moet 'afdwingen'.

- SCL is een unidirectionele lijn. Optrekken is niet nodig.

- Neem de IP-documentatie grondig door.

Stap 5: Bijgevoegde bestanden

- Alle RTL-codes van I2C Master.

- Testbank, ook I2C Slave-codes, om te testen.

- IP-documentatie.

Voor vragen kunt u gerust contact met mij opnemen:

Mitu Raj

volg mij:

Neem voor vragen contact op met: iammituraj@gmail.com

Aanbevolen:

Ontwerp van zelfstudievideogames: 6 stappen

Ontwerp van videogames: ik ben een hobbyistische game-ontwikkelaar, met mijn grootste interesses in het ontwerpen en programmeren van games. Om mijn vaardigheden te oefenen en op te frissen, maak ik af en toe eenvoudige games die ik deel met mijn vrienden en broers en zussen. Eerder zou ik de regels uitleggen aan de pla

Ontwerp van UART in VHDL: 5 stappen

Ontwerp van UART in VHDL: UART staat voor Universal Asynchronous Receiver Transmitter. Het is het meest populaire en eenvoudigste seriële communicatieprotocol. In deze instructable leert u hoe u een UART-module in VHDL ontwerpt

Hoe voldoen de uitdagingen van het ontwerp van de voeding door DC-DC Technologies: 3 stappen

Hoe komen de uitdagingen van het ontwerp van de voeding samen door DC-DC Technologies: Ik zal analyseren hoe DC-DC Technologies de uitdaging van het ontwerp van de voeding aangaat. stroom. In draagbare apparaten, hogere efficiëntie ext

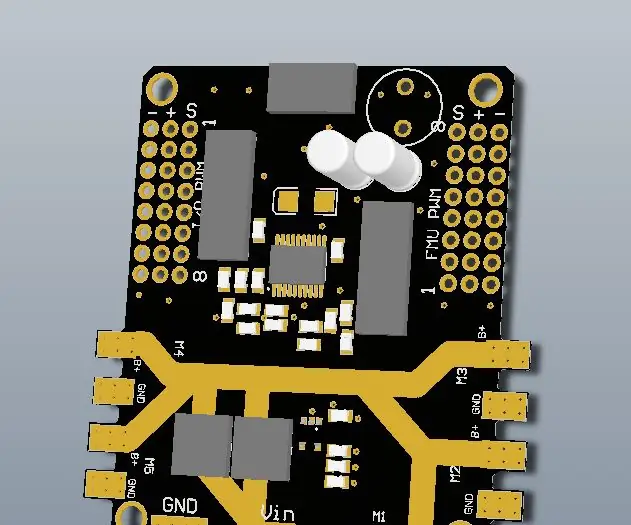

Ontwerp van een High Power PDB (Power Distribution Board) voor een Pixhawk: 5 stappen

Ontwerp van een High Power PDB (Power Distribution Board) voor een Pixhawk: een PCB om ze allemaal van stroom te voorzien! Momenteel zijn de meeste materialen die je nodig hebt om een drone te bouwen goedkoop verkrijgbaar op internet, dus het idee om een zelfontwikkelde PCB te maken is het helemaal niet waard, behalve een paar gevallen waarin je een rare en

Instructies voor het voltooien van de mock-up van het ontwerp van de rupsschuif voor het heffen/verlagen van in het midden gemonteerde voetsteunen op elektrische rolstoelen - Ajarn

Instructies voor het voltooien van de mock-up van het ontwerp van de rupsschuif voor het omhoog/omlaag brengen van in het midden gemonteerde voetsteunen op elektrische rolstoelen: in het midden gemonteerde voetsteunen kunnen omhoog worden gebracht om onder de zitting goed te worden opgeborgen en omlaag om te worden ingezet. Een mechanisme voor onafhankelijke bediening van het opbergen en plaatsen van de voetsteun is niet inbegrepen in elektrische rolstoelen op de markt, en PWC-gebruikers hebben de behoefte geuit