Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:14.

- Laatst gewijzigd 2025-01-23 15:01.

In het verleden heb ik een handleiding geschreven over het bouwen van een Z80-computer, en ik heb het circuit zo simplistisch mogelijk ontworpen, zodat het zo gemakkelijk mogelijk kan worden gebouwd. Ik heb ook een klein programma geschreven met hetzelfde idee van eenvoud. Dit ontwerp werkte redelijk goed, maar ik was er niet helemaal blij mee. Ik begon met het herschrijven van een programma ervoor waardoor het tijdens runtime kon worden geprogrammeerd. Dit was om me stukjes code te laten testen zonder het aan EEPROM te hoeven wijden, wat op zijn beurt zou vereisen dat ik de EEPROM opnieuw programmeer. Dit leek me geen leuk idee. Toen begon ik na te denken over geheugenruimtes. Als ik een stukje hardware wilde koppelen (voornamelijk IO), zou een stukje code mogelijk de hoeveelheid geheugenruimte die voor het systeem beschikbaar is, kunnen overschrijden. Onthoud dat het ontwerp alleen de lagere byte van de adresbus gebruikte en dat vervolgens de lagere bit van de hoge byte werd gebruikt om te kiezen tussen ROM- en RAM-ruimten. Dit betekende dat ik maar 253 bytes aan ruimte had om te gebruiken. Je vraagt je misschien af waarom 253 in plaats van 256. Dat komt omdat mijn nieuwe code drie bytes aan gegevens injecteert aan het einde van een geschreven programma (dit zal later worden behandeld, omdat ik het heb aangepast om aan het nieuwe ontwerp te werken).

N

Ik ging terug naar mijn oude schema's om te zien wat er nog meer aan de hand was. Ik heb een kleine fout gevonden in het geheugenselectiecircuit, dat ik zal bespreken als ik daar ben. De vereenvoudigde versie: alle schrijfverzoeken zouden daadwerkelijk doorgaan, hoewel het altijd in RAM werd geplaatst. Dit was waarschijnlijk niets om je zorgen over te maken, maar ik wilde het deze keer goed doen. En daarmee begon ik een nieuw schema te tekenen. De twee foto's die aan deze pagina zijn toegevoegd, zijn voor en na van het eigenlijke circuit. Ik heb zoveel van de spaghetti-bedrading opgeruimd, het is niet grappig.

N

Als je mijn oorspronkelijke inzending hebt gevolgd en van plan bent deze te volgen, ga je me haten. Als je fris begint, heb je geluk. Pak gewoon de onderdelen in de lijst (of hun equivalent) en volg mee.

Benodigdheden:

LM7805 - 5 Volt regelaarZ80 - de CPU; de hersenen van het systeemAT28C64B - EEPROM. "Permanente" gegevensopslag die wordt gebruikt voor de firmware van de computerIDT6116SA - SRAM; gebruikt voor het opslaan van gebruikerscode en/of algemene gegevensopslagNE555 - Systeemklok74HC374 - Octal D-Latch met /OE; gebruikt als invoerchip74LS273 - Octal D-Latch met /MR; output chipTLC59211 - LED driver chip (gebruikt zodat de 74LS273 LED's kan aansturen, aangezien hij alleen niet in staat is tot de huidige output)MC14572 - Dit is een "Line Driver" chip, maar ik vond hem perfect voor de Memory Control logica. Het heeft 4 omvormers en een NAND- en NOR-poort ingebouwd 74LS32 - Quad OF-poort CD4001 - Quad NOR-poort CD4040 - 12-traps rimpelteller; Getekende, maar niet geïmplementeerde klokverdeler (om het systeem met lagere kloksnelheden te laten werken)2 Weerstanden van 10K Ohm - Een wordt gebruikt in het 555 timercircuit, dus gebruik de waarde die u ervoor wilt hebben4 Weerstanden van 1K Ohm - Een wordt gebruikt voor de 555 timercircuit, dus gebruik wat je maar wilt. Een andere wordt gebruikt voor het aansturen van LED's, dus varieer deze ook als je wilt 8x330 Ohm Weerstand Bus8x10K Ohm Weerstand Bus11 LED's - Drie worden gebruikt voor de systeemstatus en de andere acht zijn uitgangen. Voor de 8 heb ik een staafdiagram gebruikt (HDSP-4836)4 condensatoren - Twee daarvan zijn de LM7805; 0.22uF en 0.1uF. De ene is voor de 555-timer, dus gebruik wat u denkt dat goed is. De laatste is voor power-on reset; 100uF2 N. O. Drukknoppen - De ene wordt gebruikt voor invoer, de andere voor reset8 SPST DIP-schakelaars - Gegevensinvoer; Ik gebruikte Piano Key styleWire. Heel veel draad

N

OPMERKING: de MC14572 through hole-versie is verouderd, maar de SMD-versie is nog steeds actief (zelfs niet de status "niet voor nieuw ontwerp"), dus het kan zijn dat u een printplaat moet kopen om deze te kunnen gebruiken. Een tweede 74LS32 kan worden gebruikt in plaats van de MC14572 (raadpleeg het schema van het "geheugenselectiecircuit" van de vorige versie)

Stap 1: Snel overzicht van wijzigingen + schema's

Hoe het schema te lezen: Een pijl die in een chip is gericht, is een invoer: Invoer> - Een pijl die van een chip af wijst, is een uitvoer: Uitgang <- Bussen gebruiken een lijn in plaats van een pijl: Bus |-

N

De meeste chips zijn getekend met hun exacte pinouts. Op deze chips is het dipje getekend. Op de meeste chips staan ook pinnummers en labels. Ze zijn misschien wat moeilijk te lezen. Mijn potlood werd dof.

N

In termen van circuitverbindingen is de lay-out van het nieuwe ontwerp grotendeels ongewijzigd ten opzichte van het origineel. Ik verbond de onderste nibble van de adres-high-byte met de geheugens en gebruikte toen de lage bit van de bovenste nibble (A12) voor RAM/ROM-selectie. Dit betekende dat de ROM-ruimte ging van 0000-00FF tot 0000-0FFF. De RAM-ruimte ging van 0100-01FF naar 1000-1FFF. Ik heb ook de Memory Control-logica verwisseld voor een beter ontwerp en twee nieuwe status-LED's toegevoegd (en wat lijmlogica). Ik heb ook een klokdelercircuit getekend (maar niet bedraad). Het moest twee functies vervullen. De voor de hand liggende functie is om de klokfrequentie naar beneden te verdelen. De andere functie is voor PWM (Pulse Width Modulation) doeleinden, aangezien de 555 geen golven genereert met 50% duty cycles. Dat maakt in dit circuit niet zoveel uit, maar als je de klok zou willen gebruiken om sommige LED's aan te sturen, zul je zeker de effecten merken (de ene (set van) LED('s) zal zwakker zijn dan de andere). De hele rest van het circuit is in wezen ongewijzigd.

Stap 2: CPU, geheugen en geheugenbeheer

Dit is het deel waar lezers van mijn vorige versie me haten. In de originele build gooide ik een beetje onderdelen op het bord op een plaats waar ze eruit zagen alsof ze weinig problemen zouden opleveren bij het aansluiten. Het resultaat zag eruit alsof iemand er een bord spaghetti op had gedumpt en was als "draden!" Ik wilde het een beetje opruimen, dus begon ik met het rippen van alles behalve de CPU, RAM en ROM. Ik heb bijna het hele invoercircuit, het uitvoercircuit en de lijmlogica opgehaald. Het deed me bijna pijn om te doen, maar het was nodig. Ik liet alle gegevensverbindingen intact en de lagere byte van de adresbus. Vervolgens verbond ik de volgende vier bits van de adresbus (A8-A11) met de ROM-chip. Ik zorgde ervoor dat ik deze keer om de chip heen ging om het gemakkelijker te maken om op te trekken voor herprogrammering. Ik heb ook de adresverbindingen naar de RAM-chip gesprongen.

N

Nu dat uit de weg was, moest ik nu de logica van de geheugenbesturing aansluiten. In het originele schema had ik de /MREQ-lijn van de processor rechtstreeks op /CE aangesloten op beide geheugenchips, en vervolgens heb ik /WR aangesloten op de RAM's /WE. Toen had ik de CPU's /RD en /MREQ logisch OR'd samen, evenals A9. In wezen was het zo opgezet dat alle geheugenverzoeken zowel RAM als ROM activeerden, maar A9 werd gebruikt om te selecteren welke van de chips '/OE werd geselecteerd. Dit was prima en dat allemaal omdat de chips inactief zouden blijven totdat er een geheugenverzoek werd gedaan en dan zou er slechts één /OE actief zijn tijdens een leesverzoek. Dit voorkwam overspraak, maar bracht een lastige nuance. Omdat A9 alleen werd gebruikt om te bepalen welke chip gegevens uitvoerde en omdat de CPU directe toegang had tot de /WE-pin van het RAM, zouden alle schrijfverzoeken doorgaan. Dit was oké voor de ROM omdat de schrijfmodus wordt verhinderd door /WE rechtstreeks aan de 5V-voeding te koppelen. Er zou echter naar het RAM worden geschreven, ongeacht A9. Dit betekende dat een poging tot schrijven naar een ROM-ruimtelocatie naar dezelfde locatie in de RAM-ruimte zou schrijven.

N

Een oplossing hiervoor zou zijn om de besturingslogica opnieuw te bedraden, zodat de CPU directe toegang heeft tot de /OE- en /WE-pinnen van de chips en vervolgens MREQ en A12 te gebruiken om te selecteren welke chips /CE werden aangestuurd. Ik ging voor dit idee, maar in plaats van vier NOR-poorten en een omvormer zoals het oorspronkelijke ontwerp te gebruiken, vond ik een onhandige kleine chip die perfect was voor de taak. Ik moest een circuit maken dat alleen de logische poorten gebruikte die in de chip beschikbaar waren, maar dat was eenvoudig genoeg. A12 voedt rechtstreeks in een NAND-poort en een NOR-poort. /MREQ wordt ingevoerd in de NOR-poort en het compliment wordt ingevoerd in de NAND-poort. De NAND-poort wordt gebruikt om /CE voor de RAM aan te sturen en de NOR-uitvoer wordt omgekeerd en gebruikt om de ROM /CE aan te sturen. Dit zorgt ervoor dat /MREQ laag moet zijn voordat een van beide chips wordt geselecteerd en vervolgens kiest A12 welke wordt geselecteerd. Met deze setup zullen schrijfverzoeken naar ROM nu niets meer doen. Het bespaart ook stroom omdat er maar één chip actief is in plaats van beide. Wat betreft de logische chip zelf, we hebben nog steeds twee ongebruikte omvormers erin. Eentje zal later wennen, maar we komen er wel als we er zijn.

Stap 3: Systeemstatus-LED's

Voordat ik aan dit project begon, probeerde ik verbinding te maken met een bepaald IC, maar ik had er problemen mee. Omdat ik niet zeker wist wat er aan de hand was, gebruikte ik een op het paneel gemonteerde LED om rond te tasten (een van die assemblages waarin een weerstand is ingebouwd). Hierdoor kreeg ik een nostalgisch idee dat nog steeds wordt gebruikt: status-LED's die werden gebruikt om aan te geven of er uit het geheugen werd gelezen of waarnaar werd geschreven. Het moest worden gebruikt in combinatie met de ingangs-LED die ik al had. De ingangs-LED was verbonden met de /WAIT-signaalgenerator om ons aan te geven dat het systeem, nou ja, wacht op invoer (ik kom er wel, maak je geen zorgen). Ik overwoog een LED toe te voegen om een IO-schrijfactie aan te geven, maar ik dacht dat de verandering van de output-LED's daar al een goede indicatie van zou zijn. Als ik erover nadenk, kan ik het nog toevoegen. Desalniettemin vind ik het handig om te weten of het geheugen wordt gelezen of geschreven. Nou, het is sowieso handig voor het debuggen van programma's. Ik heb er zelfs intensief gebruik van gemaakt toen ik probeerde mijn programma werkend te krijgen: waarom schrijft het naar het geheugen? Dat mag nog niet!”

N

Om deze LED's aan te sturen, heb ik de quad NOR-poort gebruikt. Ik heb alle poorten gebruikt. Er werden er slechts twee gebruikt om de statussignalen te genereren, maar de chip heeft niet de stroomcapaciteiten om de LED's daadwerkelijk aan te sturen. Ze zijn in staat om zoveel stroom te laten zinken, dus ik heb de andere twee NOR-poorten als omvormers gebruikt en de LED's als zodanig aangesloten. Omdat één LED wordt gebruikt om leesbewerkingen aan te geven en de andere voor schrijven, en een lees- en schrijfverzoek niet tegelijkertijd zal plaatsvinden, kon ik wegkomen door slechts één weerstand voor beide LED's te gebruiken. Wat betreft de signalen die ik moest decoderen, dat was ook gemakkelijk genoeg. Ik wilde dat alle geheugenleesverzoeken werden aangegeven, dus de eerste NOR-poort had /MREQ en /RD op zijn ingangen. De schrijfstatus was een beetje lastiger, maar net zo gemakkelijk. Ik gebruikte nog steeds /MREQ als één invoer, maar het gebruik van /WR als de andere zou een kleine nuance veroorzaken die ik wilde vermijden. Het zou ALLE schrijfverzoeken hebben aangegeven. Ik wilde alleen degenen die er echt doorheen gingen. Dus hoe zou ik dat doen? Weet je nog hoe ik het systeem zo heb ingesteld dat alleen het RAM kan worden geschreven? Ik gebruikte de RAM's / CE als de andere invoer naar de NOR-poort. Dit betekent dat de LED alleen oplicht wanneer RAM is geselecteerd en een schrijfverzoek wordt gedaan. In termen van LED-kleur koos ik oranje als leesindicator (maar ik vond alleen gele) en rood als schrijfindicator.

Stap 4: Invoer en uitvoer

In de vorige stap is het je misschien opgevallen dat ik al enkele van de rest van de componenten aan het bord heb toegevoegd. Ik reserveerde de ruimte, zodat ik niet per ongeluk draden zou plaatsen waar ik een onderdeel wilde hebben (dus ik zou een nieuwe locatie voor dat onderdeel moeten vinden). Je hebt misschien ook gemerkt dat ik de ingangsschakelaars op hun plaats heb gelaten en aangesloten op de stroomrail. Ik besloot dat de oorspronkelijke locatie de perfecte plek was en besloot de output-LED's in de buurt te plaatsen (hierboven). Rechts van de balkweergave bevindt zich de invoervergrendeling. Daarboven bevindt zich de uitgangsvergrendeling en links daarvan bevindt zich de LED-driver. Ik begon met het aansluiten van het display op de driver, omdat dat het gemakkelijkst was om te doen. Vervolgens heb ik de schakelaars aangesloten op de invoerzijde van de invoervergrendeling. Vervolgens verbond ik de uitvoerzijde van de uitvoervergrendeling met de LED-driver. Dit lijkt misschien een lastige opdracht om deze bedraad te krijgen, maar het was met een reden. De ingang van de uitgangsgrendel moest worden aangesloten op de databus, evenals de uitgang van de ingangsgrendel. Het idee was om de uitgangen van de input-latch te verbinden met de inputs van de output-latch, wat ik deed. Daarna hoefde ik alleen maar die rotzooi op de databus aan te sluiten. Het maakte niet uit waar deze verbindingen fysiek naartoe gingen, omdat ze allemaal elektrisch verbonden zouden zijn. De computer is nu bijna klaar.

Stap 5: Reset en voltooi invoer en uitvoer

Sorry, geen foto's voor deze stap. Raadpleeg de vorige stap voor de foto's.

N

Je hebt misschien gemerkt in de laatste foto van de vorige stap, ik had een groene knop en een andere logische chip geïnstalleerd. De chip is de OK-poort. Er worden twee poorten gebruikt om het /WAIT-signaal te genereren. Welnu, men genereert het signaal door OR-ing /IORQ en /RD van de processor. De uitvoer wordt naar de tweede poort gevoerd, waar het opnieuw wordt ge-OF'd naar een drukknop. De knop brengt de ingang van de poort hoog en dus de uitgang hoog. Deze uitvoer wordt naar de processors / WAIT-pin gevoerd. Terwijl niet ingedrukt, houdt een weerstand de ingang laag. Ik gebruikte aanvankelijk een weerstand van 10K, maar de LS32 zette eigenlijk spanning op de ingang. De weerstand liet hem niet laag genoeg vallen en ik moest hem vervangen door een 1K. Hoe dan ook, het idee is dat wanneer een IO-leesverzoek wordt gedaan, de eerste en tweede OF-poort de processor vertellen te wachten. Nadat u de invoerschakelaars hebt ingesteld op wat u maar wilt, drukt u op de knop en haalt de CPU uit de wachtstand. De groene "input"-LED, zoals ik hem in een eerdere stap noemde, is zo bedraad dat wanneer de /WAIT-pin laag wordt, deze oplicht.

N

Maar we zijn nog niet klaar. De invoerflip-flop heeft een signaal nodig om te laten weten wanneer de gegevensinvoer geldig is en naar de CPU moet worden gestuurd. Deze klokpen is actief hoog. Vroeger sloten we het gewoon aan op de knop. Dit is nog steeds een geldige optie, maar deze keer heb ik ervoor gekozen om het op dezelfde uitgang te plaatsen als de tweede OF-poort. Dit IC heeft ook een /OE-pin die moet worden aangedreven. Als het hoog zou worden gehouden, zou het nooit gegevens in de bus invoeren. Als hij laag werd gehouden, zou hij altijd de bus besturen. Om dit op te lossen, heb ik eenvoudig een derde OF-poort gebruikt. De ingangen zijn /IORQ en /RD en de uitgang gaat rechtstreeks naar de /OE van de grendel.

N

De uitgangsgrendel heeft ook de klokpen nodig om te worden aangedreven. Nogmaals, het is actief hoog. In mijn schema tekende ik de vierde OF-poort die de pin rechtstreeks aanstuurde met /IORQ en /WR. Dit betekende dat de klokpen hoog zou worden gehouden totdat er een schrijfverzoek werd gedaan, waarna deze weer laag en vervolgens weer hoog zou worden. Dit zou waarschijnlijk goed zijn geweest omdat de databus direct na de poging tot schrijven nog steeds geldige gegevens zou hebben, maar vanuit technisch oogpunt was het een afvalontwerp. Ik merkte deze fout pas op nadat ik de laatste foto's had gemaakt, maar ik heb die verbinding verscheurd en vervolgens de OF-poortuitgang ingevoerd in een van de ongebruikte omvormers van de geheugenbesturingslogica, en vervolgens de uitgang op de klokpen aangesloten. Ik heb ook het schema gerepareerd en een andere fout gevonden die ik had gemaakt. Ik heb het ook gecorrigeerd.

N

Met dat alles eindelijk gedaan, had ik een heel kleine hoeveelheid werk te doen: het resetcircuit. Ik heb een knop aan het bord toegevoegd en een weerstand van 10K gebruikt om één kant hoog te houden. De andere kant gaat rechtstreeks naar de grond. De kant die hoog wordt gehouden, is de /RESET-uitvoer, die naar elke chip ging met een /RESET-pin (de CPU en uitvoervergrendeling). Om de power-on-reset uit te voeren, heb ik een condensator toegevoegd aan de /RESET-uitgang. Het idee is dat de weerstand met grote waarde ervoor zou zorgen dat de relatief grote condensator langzaam oplaadt en de /RESET-pinnen gedurende een bepaald aantal klokcycli laag houdt (de CPU heeft vier klokcycli nodig). Je kunt waarschijnlijk al raden wat de negatieve kant van deze schakeling is. Het is hetzelfde negatieve als de vorige versie omdat het hetzelfde circuit is. Wanneer de knop wordt ingedrukt, wordt de condensator in wezen kortgesloten via de knop. Dit is slecht voor zowel de dop als de knop, dus als je je build een beetje meer permanent wilt maken, wil je hem misschien opnieuw ontwerpen. Ik dacht aan een andere 555-timer die in monostabiele modus is ingesteld. Maar daarmee is het computercircuit nu klaar. Ja. Nu moet het worden geprogrammeerd.

Stap 6: Programmeren

Dit ding programmeren was een nachtmerrie. Ik heb een Arduino EEPROM-programmeur gebouwd. Het werkte niet. Ik heb er nog een gebouwd op basis van het ontwerp en de codering van iemand anders. Werkte nog steeds niet. Ik ging terug naar de beproefde methode om de adressen en databytes handmatig in te stellen. Op de een of andere manier heb ik dat verpest. Ik heb het nog een keer geprobeerd en nog steeds fout. Ik ging nog een keer terug en ontdekte dat het een enkele byte niet was, dus ik corrigeerde het en het werkte eindelijk, godzijdank.

N

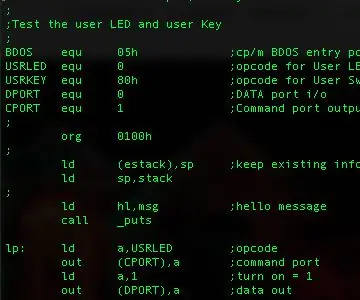

Wat het eigenlijke programma betreft, het lijkt erop dat het supercomplex en moeilijk te volgen is, maar dat is het niet. Het is eigenlijk heel simpel. De helft daarvan kopieert getallen. De andere helft wordt gedeeld tussen 16-bits wiskunde, voorwaardelijke sprongen en nog meer kopieergetallen. Dus laat me het doornemen en je vertellen hoe het werkt.

N

Initialisatie stelt slechts enkele registerwaarden in voor gebruik door het programma. De programmalus is iets complexer, maar niet heel veel. Eerst accepteert het invoer naar het A-register op poort 00. Daarna wordt het E-register naar het geheugen geschreven. Op de eerste twee lussen bevat het E-register ongewenste gegevens, dus we proberen het naar de laatste twee bytes ROM-ruimte te schrijven omdat het niet echt wordt geschreven; de adresaanwijzer (IY) wordt dan verhoogd. De waarde die is opgeslagen in D wordt vervolgens naar E verplaatst om vervolgens te worden geschreven. A wordt vervolgens geladen in D en L en E wordt gekopieerd naar H. HL is waar de waardevergelijking plaatsvindt via aftrekken en controleren van ZF (nulvlag). De eerste waarde waarmee wordt vergeleken, wordt opgeslagen in registers B en C. B en C worden behandeld als een enkel 16-bits register, BC. Als de waarden hetzelfde zijn, springt het programma rechtstreeks naar de RAM-ruimte, waar de gebruikerscode wordt verondersteld zich te bevinden. Als de code in BC geen overeenkomst is, wordt HL opnieuw geladen met de beginwaarden van D en E en opnieuw vergeleken met de waarde in SP op dezelfde manier als in BC. Als het een overeenkomst is, heeft het hetzelfde resultaat, maar worden er drie extra bytes naar het geheugen geschreven. De bytes zijn een code die ervoor zorgt dat de CPU terugspringt naar het begin van zijn programma (een software-reset). Als de tweede vergelijking echter geen overeenkomst was, gaat het programma door naar waar het een waarde van de gebruiker pakt.

N

LD SP, EDBFH; exe-code (voegt sprong toe)

N

LD IY, FFEH; initiële geheugenaanwijzer voor codeopslag

N

LD BC, EDC3H; exe-code (geen lus)

N

lus; assembler-richtlijn zodat we niet hoeven te weten waar in het geheugen dit gedeelte zich bevindt

N

IN A, (00H); programmagegevens ophalen

N

LD (IY+00H), E; E bevat code die moet worden opgeslagen

N

INC IY; naar volgende geheugenlocatie gaan

N

LD E, D; ld D in E

N

LD D, A; ld A in D

N

LDH,E; ld E in H

N

LDL,D; ld D in L

N

OF EEN; reset carry vlag

N

SBCHL, BC; geeft 0 terug als exe-code 2 is ingevoerd

N

JPZ, 1000H; zo ja, ga naar en voer het programma uit

N

LDH,E; anders ververs deze naar de juiste waarden

N

LD L, D

N

OF EEN; eerste aftrekking kan de carry-vlag hebben ingesteld. Maak het schoon

N

SBCHL, SP; geeft 0 terug als exe-code 1 is ingevoerd

N

JP NZ, lus; zo niet, herhaal het proces (begin met het verkrijgen van een waarde)

N

LD (IY+00H), C3H; injecteer anders een sprongcode aan het einde van het gebruikersprogramma

N

LD (IY+01H), 00H; jump fungeert in feite als een software-reset

N

LD (IY+02H), 00H; het is een volledige reset voor het geval registers zijn gewijzigd

N

JP1000H; ga naar en voer het gebruikersprogramma uit

Aanbevolen:

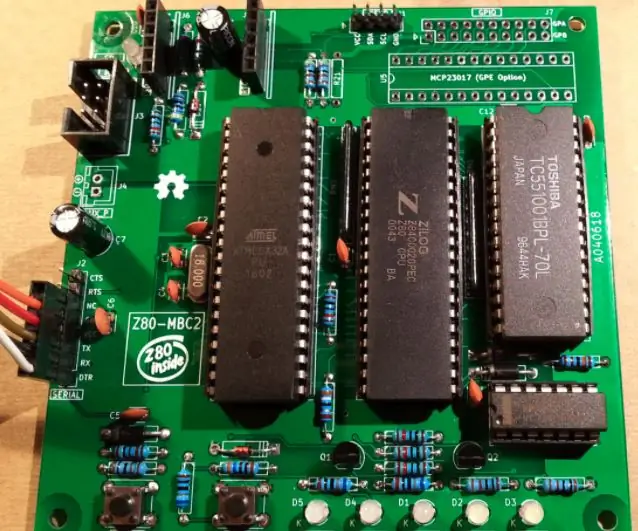

Z80 MBC2 - QP/M Bios en Loader opnieuw compileren - Ajarnpa

Z80 MBC2 - QP/M Bios en Loader opnieuw compileren: Als u zich, zoals ik, in een positie bevindt waarin u de QP/M-bios voor uw MBC2 opnieuw moet compileren, dan is dit hoe u het doet.Ik heb gedocumenteerd het proces van het opnieuw compileren van de bestaande versie. Het is aan jou om wijzigingen aan te brengen in het eigenlijke BIOS

Z80-mbc2 Z80 Code Flash gebruikers-LED - Ajarnpa

Z80-mbc2 Z80 Code Flash User LED: Dit is een voorbeeld van een gebruikers-LED-programma geschreven in Z80 assembler voor de z80-mbc2 computer. Ik heb dit een test- en revisie-oefening voor mij gedaan, dit is mijn eerste Z80-programma in meer dan 35 jaar

Z80 MBC2 - CPM2.2 BIOS opnieuw compileren - Ajarnpa

Z80 MBC2 - CPM2.2 Bios opnieuw compileren: Als u zich, zoals ik, in een positie bevindt waarin u de CP/M-bios (2.2) voor uw MBC2 opnieuw moet compileren, dan is dit hoe u het doet.In mijn geval Ik wilde het bericht "WARM BOOT" verwijderen elke keer dat een programma bestond of wanneer je een ctrl-c deed. IA

Een coole oude robot opnieuw doen: 10 stappen (met afbeeldingen)

Voer een coole oude robot opnieuw uit: maak kennis met Arlan, een leuke robot met veel persoonlijkheid. Hij woont in een natuurkundelokaal van de vijfde klas. Ik heb hem omgebouwd tot de mascotte van het robotica-team van de school, hij is ook de helper in de klas. De kinderen zien graag technologie in actie en Arlan loopt

Trainz - Inhoud opnieuw skinnen: 13 stappen

Trainz - Hoe inhoud opnieuw te skinnen: Hallo, ik heb deze handleiding gemaakt om u stap voor stap te laten zien hoe u een model voor Trainz kunt skinnen. Ik gebruik Trainz A New Era en zal het proces demonstreren met mijn gevilde CFCLA CF Class #CF4401. Ik zie dat je misschien ook moeite hebt om te villen. Het t