Inhoudsopgave:

- Stap 1: Een PWM-module-bronbestand bouwen

- Stap 2: Een PWM-module bouwen - Vivado Setup

- Stap 3: Een PWM-module bouwen - een projectbestand maken

- Stap 4: Een PWM-module bouwen - Blokontwerp en beperkingsbestandsinstelling (I)

- Stap 5: Een PWM-module bouwen - Blokontwerp en beperkingsbestandsinstelling (II)

- Stap 6: Een PWM-module bouwen - Blokontwerp en beperkingsbestandsinstelling (III)

- Stap 7: Een PWM-module bouwen - Blokontwerp en beperkingsbestandsinstelling (IV)

- Stap 8: Een PWM-module bouwen - Blokontwerp en beperkingsbestandsinstelling (V)

- Stap 9: Een PWM-module bouwen - Hardware-installatie

- Stap 10: Een PWM-module bouwen - Bitstream genereren en SDK starten

- Stap 11: Een PWM-module bouwen - Maak een nieuwe toepassing in Xilinx SDK

- Stap 12: Een PWM-module bouwen - Overzicht van de projectverkenner (I)

- Stap 13: Een PWM-module bouwen - Overzicht van de projectverkenner (II)

- Stap 14: Een PWM-module bouwen - Overzicht van de projectverkenner (III)

- Stap 15: Een PWM-module bouwen - PWM-functie inpakken (I)

- Stap 16: Een PWM-module bouwen - PWM-functie inpakken (II)

- Stap 17: Een PWM-module bouwen - PWM-functie inpakken (III)

- Stap 18: Een PWM-module bouwen - laat het draaien

- Stap 19: Videoverwerking streamen op Digilent ZYBO met OV7670

- Stap 20: Compleet blokdiagram

- Stap 21: Sluit de OV7670 aan op de ZYBO

- Stap 22: Blokontwerp maken

- Stap 23: VHDL-bestanden toevoegen voor OV7670-camerabediening en -opname

- Stap 24: Bestand met beperkingen toevoegen

- Stap 25: IP-opslagplaats toevoegen voor HLS IP

- Stap 26: Modules en IP toevoegen

- Stap 27: IP-configuratie-instellingen

- Stap 28: PS IP-blok toevoegen en configureren

- Stap 29: Deel 1. Een PWM-module bouwen voor servomotoren

- Stap 30: Video-ingangsaansluitingen (aclk gemarkeerd)

- Stap 31: Verbindingen met OV7670

- Stap 32: Aansluitingen op Video Out Side

- Stap 33: Blok- en verbindingsautomatisering uitvoeren

- Stap 34: HDL-wrapper genereren

- Stap 35: Bitstream genereren, hardware exporteren naar SDK, SDK starten vanuit Vivado

- Stap 36: SDK (geen FreeRTOS)

- Stap 37: FreeRTOS-implementatie

- Stap 38: Gebruiksinstructies

- Stap 39: Referenties en links

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:19.

- Laatst gewijzigd 2025-01-23 15:01.

Begin bij stap één voor details over het maken van een 2-assige servo PWM-controller.

Begin bij het enorme blokschema (stap 19) voor het volledige project.

Camera + Pan/tilt-opstelling die we gebruikten:

De PmodCON3 van Digilent werd gebruikt om de servo's aan te sluiten.

Stap 1: Een PWM-module-bronbestand bouwen

Stap 2: Een PWM-module bouwen - Vivado Setup

Download eerst de Vivado Design Suite van de Xilinx-website. Installeer alle ontwerpsuites, inclusief Vivado Software Development Kit (SDK). Dit project gebruikt versie 2017.2.

In de tussentijd zou Digilent Adept 2 ook moeten worden geïnstalleerd als een Zybo-bordstuurprogramma.

Stap 3: Een PWM-module bouwen - een projectbestand maken

Voordat u een projectbestand maakt, moet u ervoor zorgen dat u het Zybo-bestand al correct hebt geïnstalleerd als de tutorial hier:

Vivado-versie 2015.1 en later Board-bestandsinstallatie

Open Vivado 2017.2. Klik bij Quick Start op Project maken -> Volgende -> Projectnaam (noem hier uw projectnaam) -> Projecttype. Selecteer bij Projecttype RTL-project en markeer op dit moment geen bronnen. Selecteer vervolgens voor het standaardgedeelte "Boards" en "Zybo" als weergavenaam. Klik vervolgens op Voltooien om het project te starten.

Stap 4: Een PWM-module bouwen - Blokontwerp en beperkingsbestandsinstelling (I)

Klik in Flow Navigator op ""Blokontwerp maken" en druk vervolgens op OK. klik op het "+" teken om de benodigde IP's toe te voegen. Toevoegen:

- Eén ZYNQ7-verwerkingssysteem Twee AXI-timers

- Twee AXI-timer

Stap 5: Een PWM-module bouwen - Blokontwerp en beperkingsbestandsinstelling (II)

Voer na het toevoegen van IP's Block Automation en verbindingsautomatisering uit. Zodra de automatisering is voltooid, klikt u in het blok "axi_timer_0" met de rechtermuisknop op pwm0 -> Extern maken. Noem de pwm0 externe pin als pwm_Xaxis. Herhaal ook het bovenstaande proces op het blok "axi_timer_1" en noem de pwm0 externe pin als pwm_Zaxis.

Stap 6: Een PWM-module bouwen - Blokontwerp en beperkingsbestandsinstelling (III)

Merk op dat elke keer dat we het blokontwerp in Vivado voltooien, we een HDL-wrapper moeten maken. Omdat het de module op het hoogste niveau voor elk project zal zijn.

Stap 7: Een PWM-module bouwen - Blokontwerp en beperkingsbestandsinstelling (IV)

Nu moeten we ons beperkingsbestand instellen om pinnen toe te wijzen die zijn verbonden met ons blokschema. Sluit het Block Design-venster, op het tabblad Bronnen, "Bronnen toevoegen"->Beperkingen toevoegen of maken-> voeg de Zybo-Master.xdc toe als onze beperkingsbestanden.

Stap 8: Een PWM-module bouwen - Blokontwerp en beperkingsbestandsinstelling (V)

Open het beperkingsbestand Zybo-Master.xdc vanuit de map Constraints, verwijder de opmerkingen over de poorten die we willen specificeren als uitgangssignalen en hernoem " get_ports{XXXX}", waarbij XXXX de externe pin aanduidt die in het blokdiagram wordt genoemd. De instelling van het beperkingsbestand wordt weergegeven in de afbeelding.

Stap 9: Een PWM-module bouwen - Hardware-installatie

Sluit de servomotoren aan op de Pmod CON3. TowerPro SG90 is het servomotormodel dat we in dit project hebben gebruikt. Voor de servomotordraden vertegenwoordigt de oranje draad het PWM-signaal, aangesloten op de SIG-pin in Pmod CON3. De rode draad Vcc is een stroomdraad die is aangesloten op de VS-pin in Pmod CON3. Ten slotte is de bruine draad Gnd een aardingsdraad die is aangesloten op de GND-pin. Plaats vervolgens de Pmod CON3 in de bovenste rij van de JD-poort in het Zybo-bord.

Stap 10: Een PWM-module bouwen - Bitstream genereren en SDK starten

1. Voer op het tabblad Project Navigator BitStream genereren uit.

2. Hardware exporteren: Bestand > Exporteren > Hardware exporteren-> markeer "bitstream opnemen"-> OK 3. Start SDK: Bestand -> SDK starten.

Stap 11: Een PWM-module bouwen - Maak een nieuwe toepassing in Xilinx SDK

Maak een Nieuwe Applicatie:

Bestand > Nieuw > Toepassingsproject -> Voer de naam van uw project in -> Voltooien

Onder Project Explorer zouden er drie mappen moeten zijn.

In dit geval is "design_1_wrapper_hw_platform_0" de map die eerder door Vivado is geëxporteerd. Axis_2_PWM_SDK_bsp is de map voor het ondersteuningspakket van het bord. En Axis_2_PWM_SDK is onze hoofdprojectmap in SDK. U kunt het bestand "helloworld.c" zien in de map "src" van Axis_2_PWM_SDK, waarbij "helloworld.c" het hoofdbestand is.

Stap 12: Een PWM-module bouwen - Overzicht van de projectverkenner (I)

Laten we enkele bestanden controleren onder Project Explorer. Open eerst in de map "design_1_wrapper_hw_platform_0" de "system.hdf". Dit bestand demonstreert de adreskaart voor processor ps7_cortex9 en de IP-blokken die aanwezig zijn in ons ontwerp.

Stap 13: Een PWM-module bouwen - Overzicht van de projectverkenner (II)

Controleer vervolgens het bestand "include" en "libsrc" in de map "de Axis_2_PWM_SDK_bsp". Bibliotheekbestanden hier stellen ons in staat om te communiceren met hardware-randapparatuur zonder registers te "afspelen".

Stap 14: Een PWM-module bouwen - Overzicht van de projectverkenner (III)

Via de BSP-documentatie wordt xtmrctr.h gevonden als een Xilinx Timer Control Library gerelateerd aan AXI Timer. Meestal zouden we hier de gewenste PWM-functie kunnen vinden. Als u echter de documentatie "tmrctr_v4_3" leest, blijkt dat het stuurprogramma momenteel de PWM-werking van het apparaat niet ondersteunt. Vanwege de tekortkoming in de PWM-functie, moeten we onze PWM-functie afronden met behulp van xtmrctr.h en AXI Timer v2.0 LogiCORE IP Product Guide.

Stap 15: Een PWM-module bouwen - PWM-functie inpakken (I)

Terug naar het hoofdbestand "helloworld.c", neem de volgende header-bestanden op:

Stap 16: Een PWM-module bouwen - PWM-functie inpakken (II)

Definieer de basisadressen van twee AXI TIMErs via "xparameters.h".

Stap 17: Een PWM-module bouwen - PWM-functie inpakken (III)

Bouw de gewenste PWM-functie.

Duty_val: zet de graadwaarde om in duty cycle. PWM_Freq_Duty: stel de gewenste frequentie en duty cycle in om PWM te genereren. Er moet ook een klokperiode worden toegewezen.

PWM_START: wijs het PWM-registeradres toe en begin met het genereren van PWM.

PWM_STOP: wijs het PWM-registeradres toe en stop met het genereren van PWM.

De rest van de democode wordt weergegeven in "helloworld.c" onder "Axis_2_PWM_SDK"

Stap 18: Een PWM-module bouwen - laat het draaien

1. Programmeer de FPGA via SDK

- Sluit de Zybo Board via de USB-poort aan op de pc.

- Xilinx Tools -> Programma FPGA

2. Voer het programma uit:

Klik op het pictogram "Uitvoeren" en drop-down het menu -> Uitvoeren als -> Starten op hardware

3. SDK-terminal

- Open de SDK-terminal -> Verbinden met seriële poort -> OK

- Voer het programma uit. Als de democode succesvol is uitgevoerd, zou u "Initialisatie voltooid!" moeten zien. op de SDK-terminal.

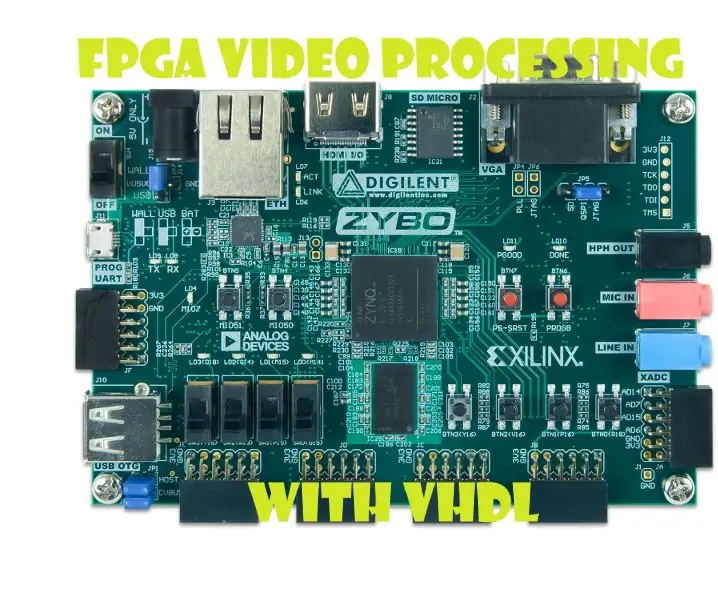

Stap 19: Videoverwerking streamen op Digilent ZYBO met OV7670

Compleet archiefbestand bijgevoegd.

Stap 20: Compleet blokdiagram

Dit toont het volledige diagram van alle verbindingen en IP-blokken in het project

Stap 21: Sluit de OV7670 aan op de ZYBO

Maak een verbinding om de ov7670-module aan te sluiten op de ZYBO Pmods

Gegevens Pmod is Pmod D

Controle Pmod is Pmod C

Sluit bovendien de PmodCON3 en servo's aan zoals gespecificeerd in de eerste helft van deze tutorial

Stap 22: Blokontwerp maken

Klik in Flow Navigator op "Blokontwerp maken" en druk vervolgens op OK.

Stap 23: VHDL-bestanden toevoegen voor OV7670-camerabediening en -opname

Voeg de VHDL-bestanden die aan deze stap zijn toegevoegd toe aan het project

Stap 24: Bestand met beperkingen toevoegen

Voeg het bijgevoegde beperkingenbestand toe aan uw project.

Stap 25: IP-opslagplaats toevoegen voor HLS IP

Neem het bijgevoegde Zip-bestand en pak het uit in een nieuwe map met dezelfde naam in een nieuwe map (map) genaamd "HLS_repo".

Voeg een IP-repository toe aan uw project door naar de IP-catalogus te gaan en met de rechtermuisknop te klikken op "Add Repository…"

Navigeer naar uw map "HLS_repo" en selecteer deze.

Optioneel: Maak zelf het HLS-videoverwerkingsblok aan!

Stap 26: Modules en IP toevoegen

Voeg de modules ov7670_axi_stream_capture, debounce en ov7670_controller toe aan het blokschema door met de rechtermuisknop op de achtergrond te klikken en "Module toevoegen…" te selecteren.

Voeg op dezelfde manier de IP's toe:

- HLS_Video_Track

- Schrijven naar videoframebuffer

- Videoframebuffer lezen

- Videotimingcontroller

- AXI4-Stream naar video-uitgang

- 3 van "Plakje"

- Constante

- 2 van AXI-timer

Stap 27: IP-configuratie-instellingen

Zoals op de foto's te zien is

Stap 28: PS IP-blok toevoegen en configureren

Voeg het ZYNQ7-verwerkingssysteem toe aan het blokschema

bewerk de configuratie:

-

PS-PL-configuratie

-

HP

- Schakel S HP 0. in

- Schakel S HP 1. in

-

-

Klok configuratie

-

PL stoffen klokken

- FCLK_0 bij 100MHz

- FCLK_1 op 25MHz (OutputClock)

- FLCK_2 bij 35MHz (<=50MHz) (CameraClock)

-

Stap 29: Deel 1. Een PWM-module bouwen voor servomotoren

Breng axi_timer_0 pwm0 naar de nieuwe uitvoerpoort pwm_Xaxis

Breng axi_timer_1 pwm0 naar de nieuwe uitvoerpoort pwm_Zaxis

Stap 30: Video-ingangsaansluitingen (aclk gemarkeerd)

Sluit de video-ingangszijde IP-blokken correct aan

(* deze verbindingen moeten worden gemaakt door de juiste opties te selecteren tijdens verbindingsautomatisering) "aclk" van de axi_stream_capture gaat naar:

- ap_clk op videoframebuffer schrijven

- ap_clk op HLS-videostreamverwerkingsblok

- *aclk op AXI smartconnect IP van de videoframebuffer Schrijf naar de S_AXI_HP0

- *aclk komt overeen met de kanalen van de AXI Interconnect IP voor de S_AXI-kanalen van het HLS-videoverwerkingsblok en de videoframebuffer schrijft S_AXI_HP0_ACLK op het PS-blok

Het videostreamsignaal wordt eenvoudig in serie geschakeld van het opnameblok naar de Zynq-geheugeninterface.

- Video gaat van opnameblok naar HLS-verwerkingsblok.

- De verwerkte video van het HLS-blok gaat naar het framebufferschrijfblok.

- *Het framebufferschrijfblok maakt verbinding met de HP0-interface op het Zynq PS-blok.

- Het m_axis_tuser-signaal van de uitvoer van het opnameblok wordt handmatig aangesloten op zowel het video_in_TUSER-invoersignaal op het HLS-verwerkingsblok als het ap_start-signaal op hetzelfde blok.

Het TUSER-signaal (tuser) wordt gebruikt door het AXI-videostreamprotocol om het begin van een frame van de video aan te geven. AP_Start vertelt het HLS-blok om te beginnen met verwerken. We gebruiken dus tuser om het HLS-blok te activeren om elk frame te verwerken zoals het is komt binnen. Bij het aansluiten van een enkel signaal van een bus en het op deze manier afsplitsen is het noodzakelijk om dit ook op het normale eindpunt van de rest van de bus aan te sluiten. Vivado gaat ervan uit dat als u het signaal handmatig aansluit, u wilt loskoppelen waar het normaal gesproken verbinding mee zou maken.

Configuratie-instellingen van IP-blokken:

Videoframebuffer schrijven:

Videoformaten: RGB8

1 monster per klok Max. kolommen: 1280 (>=640) Max. rijen: 960 (>=480) Max. gegevensbreedte: 8

Stap 31: Verbindingen met OV7670

Op het blok ov7670_axi_stream_capture

- Maak alle ingangen extern (klik met de rechtermuisknop op een speld en selecteer in het menu, of klik met de linkermuisknop->ctrl+T)

- Laat de namen zoals ze zijn

Op het blok ov7670_controller

- Maak alle blokuitgangen extern

- Hernoem de poort config_finished naar led0

- sluit clk aan op de CameraClock (<=50MHz) (FCLK_2)

Op het debounce-blok

- sluit de button1-ingang aan op een externe ingangspoort genaamd btn0

- sluit de out1 aan op de resend-lijn op het ov7670_controller IP-blok

- sluit de button2-ingang aan op een externe ingangspoort genaamd btn3

- sluit de out2n aan op de ext_reset_in-ingang op het Processor System Reset IP voor het video-opnameklokdomein. (*Dit moet mogelijk worden gedaan nadat het IP-adres is gegenereerd*)

- sluit clk aan op de CameraClock (<=50MHz) (FCLK_2)

Stap 32: Aansluitingen op Video Out Side

Aansluitingen voor blokken Video Timing Controller (VTC), AXI4-Stream to Video Out en slices

- Gebruik 25MHz klok (FCLK_1) voor vid_io_out_clk en VTC clk

- Gebruik 100MHz klok (FCLK_0) voor aclk op AXI4-Stream to Video Out

- vtiming_out naar vtiming_in

- Video Frame Buffer Lezen m_axis_video gaat naar AXI4-Stream naar Video Out video_in

- vtg_ce gaat naar gen_clken

- Bind VTC clken, aclken, vid_io_out_ce aan Constant dout[0:0]

- Breng vid_hsync en vid_vsync naar respectievelijk externe uitgangspoorten vga_hs en vga_vs. (niet afgebeeld)

Plakken:

-

Plakjes moeten worden ingesteld zoals weergegeven in bijgevoegde afbeeldingen

- hernoem de blokken naar slice_red, slice_green en slice_blue

- stel slice-bereiken in zoals weergegeven in de afbeeldingen volgens de naam van het blok

- sluit elke slice-uitgang aan op een externe poortuitgang zoals weergegeven in de afbeelding.

- vid_data[23:0] maakt verbinding met de ingangen voor elke slice (Din[23:0])

Stap 33: Blok- en verbindingsautomatisering uitvoeren

Voer Block Automation uit om de dingen van het ZYNQ7 PS-blok te verbinden. Zoals blijkt uit foto.

Voer verbindingsautomatisering uit om alle interconnectie-IP's te maken. Besteed veel aandacht aan alle opties in elke foto.

Verbind out2n op het debounce-blok met het video-opnameklokdomein Processorsysteem Reset ext_reset_in input.

Stap 34: HDL-wrapper genereren

Genereer de HDL Wrapper voor uw blokontwerp.

Stel het in als de bovenste module.

Stap 35: Bitstream genereren, hardware exporteren naar SDK, SDK starten vanuit Vivado

Zorg ervoor dat u bitstream opneemt in de export.

Het genereren van bitstream kan erg lang duren.

Start vervolgens SDK

Stap 36: SDK (geen FreeRTOS)

Deze versie doet alles zonder FreeRTOS te gebruiken, waardoor de code mooi wordt gecondenseerd.

Maak een standalone BSP op basis van het hardware-ontwerp. De standaardopties zouden goed moeten zijn. Zorg ervoor dat BSP-bronnen zijn gegenereerd.

Maak een app zoals weergegeven in afbeelding. (lege applicatie)

Verwijder de automatisch gegenereerde hoofdmap en importeer de bijgevoegde bestanden.

Stap 37: FreeRTOS-implementatie

Deze versie maakt gebruik van FreeRTOS. Maak een FreeRTOS901 BSP op basis van het hardware-ontwerp. De standaardopties zouden goed moeten zijn. Zorg ervoor dat BSP-bronnen zijn gegenereerd.

Maak een app zoals weergegeven in afbeelding. (lege applicatie)

Verwijder de automatisch gegenereerde hoofdmap en importeer de bijgevoegde bestanden.

Stap 38: Gebruiksinstructies

Dit project is een beetje lastig om te starten. Volg de stappen in volgorde.

Zorg ervoor dat uw ZYBO niets zelf laadt wanneer deze wordt ingeschakeld. Dit betekent dat de Done LED niet mag oplichten. Een manier om dit te doen is door de opstartbronjumper in te stellen op JTAG.

Open het project (FreeRTOS of niet) dat u wilt programmeren vanuit SDK

- Zet uw ZYBO aan. De Done-LED mag niet oplichten.

- Programmeer de FPGA met het bitbestand. De Klaar-LED moet oplichten. Led0 mag niet oplichten.

- Voer de code uit (vergeet niet om voorbij het startonderbrekingspunt te gaan als u dat doet).

Op dit punt zou u een uitvoer op uw VGA-scherm moeten krijgen.

Om opnieuw op te starten (als het bugs of wat dan ook): tik snel op de PS-SRST-knop of zet de ZYBO uit en weer aan. Ga verder vanaf stap 2.

Als u de processor stopt met de debugger, blijft de camera in positie in plaats van te bewegen. De videostream gaat sowieso door.

Stap 39: Referenties en links

Xilinx referentiegidsen en documentatie:

- PG044 - AXI-stream naar video-uitgang

- PG278 - Videoframebuffer lezen/schrijven

Andere links:

- Lauri's blog - VDMA input

- Lauri's blog - OV7670 naar VGA-uitgang met BRAM

- Hamsterworks-wiki, door Mike Fields, de originele bron van de OV7670-code

- Gegevensblad met basisspecificaties voor timing

Aanbevolen:

Aan de slag met de M5StickV AI + IOT-camera: 6 stappen (met afbeeldingen)

Aan de slag met de M5StickV AI + IOT-camera: kort overzicht De M5StickV is een kleine AI + IOT-camera met een diameter van bijna 2 munten. degelijke specificaties. De camera wordt aangedreven door ongelooflijke

GEMOTORISEERDE CAMERA SLIDER MET TRACKING SYSTEEM (3D geprint): 7 stappen (met afbeeldingen)

GEMOTORISEERDE CAMERASCHUIF MET TRACKINGSYSTEEM (3D-geprint): In principe zal deze robot een camera/smartphone op een rail verplaatsen en een object "volgen". De locatie van het doelobject is al bekend bij de robot. De wiskunde achter dit volgsysteem is vrij eenvoudig. We hebben een simulatie gemaakt van het volgproces

Videoverwerking met VHDL en een Zybo: 10 stappen

Videoverwerking met VHDL en een Zybo: FPGA's zijn sneller te verwerken dan CPU's, omdat ze veel parallel kunnen rekenen. Opmerking: dit project is nog in aanbouw en zal worden verbeterd (zodra ik tijd heb). Ondertussen reis ik de wereld rond

Toetsenbord Tilt Lifter.: 3 stappen

Keyboard Tilt Lifter.: Ik heb onlangs een "light up" toetsenbord van Belkin gekocht, maar was een beetje verbijsterd toen ik ontdekte dat de kleine pootjes die je normaal gebruikt om de kanteling van het toetsenbord aan te passen niet in het ontwerp zijn opgenomen. Omdat ik een hekel heb aan typen op een plat toetsenbord, besluit ik

Gitaarversterker Tilt Stand - Easy As Lincoln Logs - Klein, draagbaar, eenvoudig, stabiel, goedkoop of gratis: 9 stappen

Kantelstandaard voor gitaarversterker - zo eenvoudig als Lincoln Logs - Klein, draagbaar, eenvoudig, stabiel, goedkoop of gratis: Kantelstandaard voor gitaarversterkers - zo eenvoudig als lincoln-stammen. klein, draagbaar, eenvoudig, stabiel, goedkoop of gratis met behulp van multiplex. Geweldig voor combo-versterkers, groter ontwerp kan worden gebruikt voor open achterkanten