Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:16.

- Laatst gewijzigd 2025-01-23 15:01.

Ik word overweldigd door het soort reacties dat ik krijg op deze blog. Bedankt jongens voor het bezoeken van mijn blog en het motiveren van mij om mijn kennis met jullie te delen. Deze keer ga ik het ontwerp presenteren van een andere interessante module die we in alle SOC's zien - Interrupt Controller.

We gaan een eenvoudige maar krachtige Programmable Interrupt Controller ontwerpen. Het is een volledig configureerbaar en geparametriseerd ontwerp dat over verschillende platforms kan worden overgedragen. Ik heb dit ontworpen nadat ik veel had gelezen over een aantal populaire interruptcontroller-architecturen die er zijn, zoals NVIC, 8259a, RISC-V PLIC, Microblaze's INTC enz. Ik hoop dat jullie deze blog nuttig vinden en je helpen een idee te krijgen van hoe interrupts worden afgehandeld door een processor met de hulp van een Interrupt Controller.

Stap 1: Specificaties:

Hieronder volgen de specificaties van het IP:

- AHB3-Lite-interface.

-

Statisch configureerbare parameters:

- Aantal externe onderbrekingsbronnen; ondersteunt tot 63 interrupts.

- Aantal prioriteitsniveaus; ondersteunt tot 63 niveaus.

- Aantal nestniveaus; ondersteunt tot 8 niveau van nesten.

- Bus breedte; 32 of 64.

- Wereldwijd en lokaal maskeerbare interrupts.

- Dynamisch configureerbaar prioriteitsniveau voor elke onderbreking.

- Twee modi: volledig geneste modus en gelijke prioriteitsmodus.

- Ondersteunt actieve, gevoelige interrupts op hoog niveau.

RISC-V PLIC specificaties geïnspireerd interrupt handshaking mechanisme wordt gebruikt in het ontwerp.

Interrupt pre-emption is geïnspireerd op 8259a

Andere leest: Microblaze INTC, NVIC

Stap 2: Overzicht van PIC

Programmable Interrupt Controller (PIC) ontvangt meerdere interrupts van externe randapparatuur en voegt deze samen in een enkele interrupt-uitgang naar een doelprocessorkern.

PIC wordt aangestuurd via controle- en statusregisters. Alle PIC-registers zijn in het geheugen toegewezen en zijn toegankelijk via de AHB3-Lite-businterface.

De registerbank bestaat uit configuratieregister, activeringsregisters, lopende registers, in-service registers, prioriteitsregisters en ID-register, die typisch zijn in Interrupt Controllers.

Configuratieregister wordt gebruikt om de werkingsmodus van PIC in te stellen. Het kan werken in de volledig geneste modus of in de modus met gelijke prioriteit.

Aan elke interrupt kunnen prioriteiten worden toegewezen en afzonderlijk worden gemaskeerd. Globale maskering van alle interrupts wordt ook ondersteund.

De registerbank werkt samen met Priority Resolver en BTC (Binary-Tree-Comparator) om de prioriteiten van wachtende interrupts op te lossen en dienovereenkomstig de interrupt aan de processor te bevestigen. ID-register bevat de ID van de in afwachting van onderbreking met de hoogste prioriteit.

Stap 3: RTL Ontwerp en Implementatie

Het ontwerp van PIC legt de nadruk op het verminderen van de latentie van het oplossen van prioriteiten, wat het meest tijdkritische onderdeel van het ontwerp is. Omdat het ontwerp prioriteiten oplost in een enkele klokcyclus, nemen de prestaties af met de toename van het aantal bronnen met een Log2-complexiteit.

Het ontwerp is met succes geïmplementeerd en de timing is geverifieerd tot aan de volgende frequenties op Artix-7 FPGA's.

- Tot 15 bronnen: 100 MHz

- Tot 63 bronnen: 50 MHz

Interrupt Latency toegevoegd door PIC alleen is 3 klokcycli (exclusief de contextomschakeltijd van de processor en de eerste ISR-instructie-ophaaltijd).

Stap 4: Belangrijke opmerkingen en bijgevoegde bestanden

Belangrijke aantekeningen:

- Als de AHB3-Lite-interface ongewenst is, kunt u de bovenste module wijzigen en het skeletontwerp van PIC gebruiken. De meegeleverde testbank is echter voor IP met AHB3-Lite-interface.

- PIC IP v1.0 is een volledig draagbaar, kaal RTL-ontwerp.

- Functioneel geverifieerd om op beide modi te werken.

Bijgevoegde bestanden:

- Ontwerp codes en testbench in VHDL.

- Volledige IP-documentatie.

Het is een open-source ontwerp … Voel je vrij om te gebruiken …

Voor vragen, op elk moment:

Mitu Raj

Aanbevolen:

Ontwerp van UART in VHDL: 5 stappen

Ontwerp van UART in VHDL: UART staat voor Universal Asynchronous Receiver Transmitter. Het is het meest populaire en eenvoudigste seriële communicatieprotocol. In deze instructable leert u hoe u een UART-module in VHDL ontwerpt

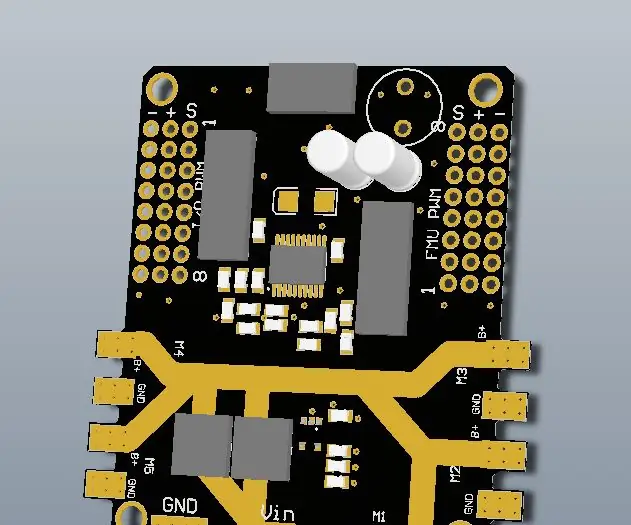

Ontwerp van een High Power PDB (Power Distribution Board) voor een Pixhawk: 5 stappen

Ontwerp van een High Power PDB (Power Distribution Board) voor een Pixhawk: een PCB om ze allemaal van stroom te voorzien! Momenteel zijn de meeste materialen die je nodig hebt om een drone te bouwen goedkoop verkrijgbaar op internet, dus het idee om een zelfontwikkelde PCB te maken is het helemaal niet waard, behalve een paar gevallen waarin je een rare en

Ontwerp en realisatie van een oriëntatiesysteem voor fotovoltaïsche panelen: 5 stappen

Ontwerp en realisatie van een oriëntatiesysteem van fotovoltaïsche panelen: ontwerp en realisatie van een oriëntatiesysteem van fotovoltaïsche panelen

Een batterijpakket van 4,5 volt maken van een batterij van 9 V: 4 stappen

Een 4,5 volt batterijpakket maken van een 9V-batterij: deze instructie gaat helemaal over het splitsen van een 9V-batterij in 2 kleinere 4,5V-batterijpakketten. De belangrijkste reden om dit te doen is 1. Je wilt 4,5 volt 2. Je wilt fysiek iets kleiners dan een 9V batterij

Instructies voor het voltooien van de mock-up van het ontwerp van de rupsschuif voor het heffen/verlagen van in het midden gemonteerde voetsteunen op elektrische rolstoelen - Ajarn

Instructies voor het voltooien van de mock-up van het ontwerp van de rupsschuif voor het omhoog/omlaag brengen van in het midden gemonteerde voetsteunen op elektrische rolstoelen: in het midden gemonteerde voetsteunen kunnen omhoog worden gebracht om onder de zitting goed te worden opgeborgen en omlaag om te worden ingezet. Een mechanisme voor onafhankelijke bediening van het opbergen en plaatsen van de voetsteun is niet inbegrepen in elektrische rolstoelen op de markt, en PWC-gebruikers hebben de behoefte geuit