Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:16.

- Laatst gewijzigd 2025-01-23 15:01.

Ons doel met dit project was om iets te creëren dat gemeenschappen energie en financiële middelen zou besparen. Door beweging geactiveerde straatverlichting zou beide dingen doen. Overal in het land wordt energie verspild aan straatverlichting die straten verlicht die leeg zijn. Ons straatverlichtingssysteem zorgt ervoor dat de lichten alleen aan zijn als dat nodig is, wat gemeenschappen talloze dollars bespaart. Met behulp van bewegingssensoren schakelt het systeem de verlichting alleen in als er auto's aanwezig zijn. Ook voor de veiligheid van voetgangers hebben we een uitschakelknop geïmplementeerd die alle lichten op straat aanzet. De volgende stappen laten u zien hoe we ons verkleinde model van het project hebben ontworpen en gebouwd met behulp van Vivado en een Basys 3-bord.

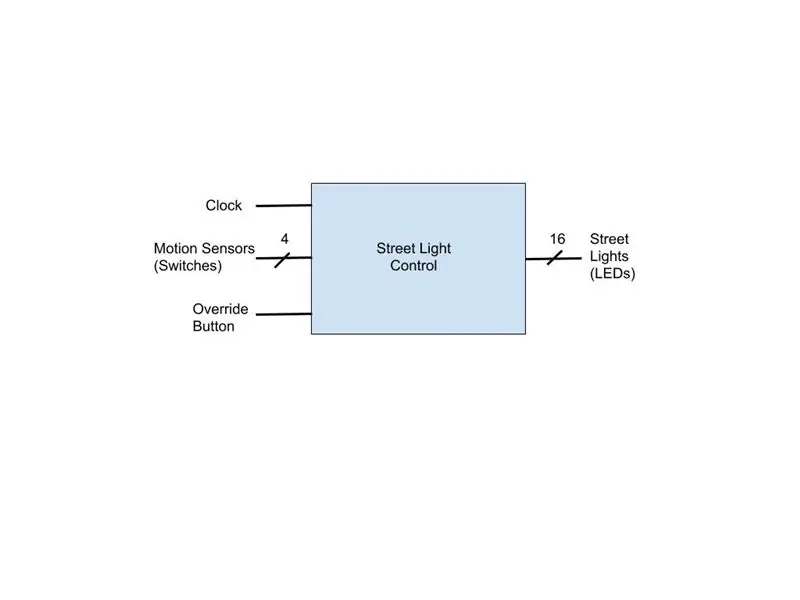

Stap 1: Systeem Black Box

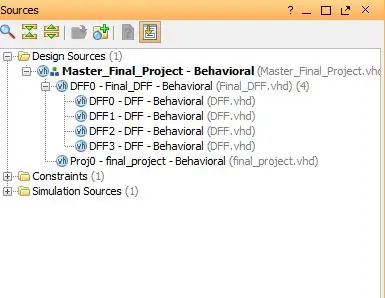

We begonnen dit project met het tekenen van een eenvoudig black box-diagram. Een black box-diagram toont eenvoudig de inputs en outputs die ons systeem nodig heeft om alle noodzakelijke processen te voltooien. We hebben geprobeerd ons ontwerp zo eenvoudig en eenvoudig mogelijk te houden. Onze drie systeemingangen omvatten een bus met bewegingssensoren (4 voor ons verkleinde model), een voetgangersoverride-knop en een klokingang. Aan de andere kant is onze enkele uitgang een bus met LED-verlichting die onze straatverlichting vertegenwoordigt. Voor dit model hebben we een scenario van 16 straatlantaarns gebruikt, simpelweg omdat dat het maximale aantal ingebouwde LED-uitgangen is op het Basys 3-bord. Ten slotte konden we met behulp van dit diagram ons Vivado-project, bron- en beperkingsbestanden maken met de juiste invoer en uitvoer.

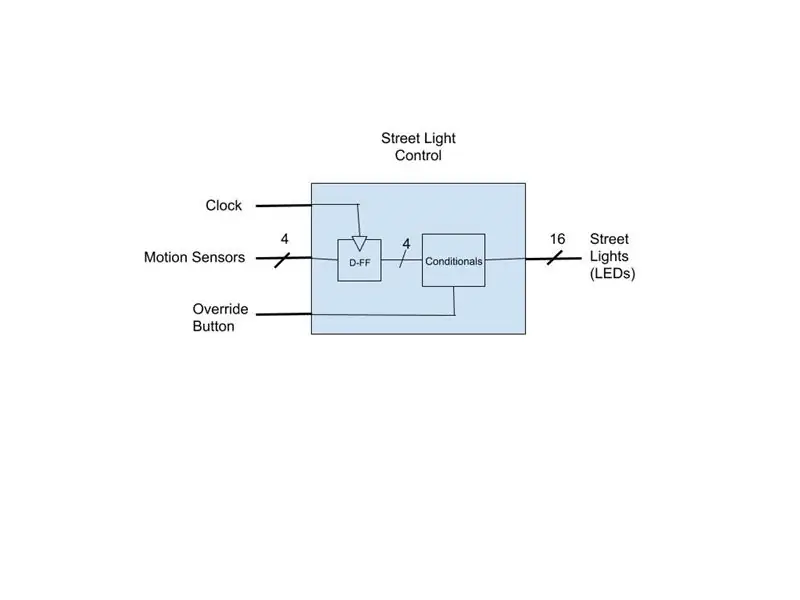

Stap 2: Componenten

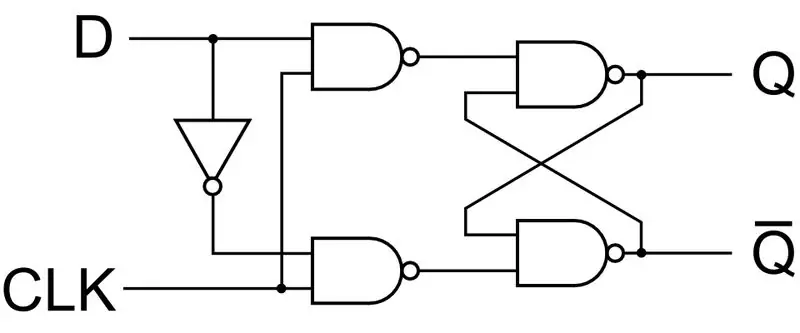

In deze stap gaan we dieper in op de componenten waaruit ons black box-diagram bestaat. Ons eerste onderdeel is een VHDL-bronbestand met D-flip-flops. D-flip-flops nemen gewoon het signaal dat wordt ingevoerd door de sensoren op de stijgende flank van de klok, en houden die gegevens vast tot de volgende stijgende flank. Dit voorkomt dat onze gevoelige bewegingssensoren ervoor zorgen dat de output-LED's "flikkeren". We hebben ook een enkele D-flip-flop op het ingangssignaal van de knop geplaatst om de LED's ongeveer 5-7 seconden aan te houden nadat de knop is ingedrukt. We hebben dit ook door een klokverdeler geleid.

entiteit clk_div2 is Port (clk: in std_logic; sclk: uit std_logic); einde clk_div2;

architectuur my_clk_div van clk_div2 is

constante max_count: geheel getal:= (300000000); signaal tmp_clk: std_logic:= '0'; begin my_div: proces (clk, tmp_clk) variabele div_cnt: geheel getal:= 0; begin if (rising_edge(clk)) then if (div_cnt = MAX_COUNT) then tmp_clk <= not tmp_clk; div_cnt:= 0; anders div_cnt:= div_cnt + 1; stop als; stop als; sclk <= tmp_clk; eindproces my_div; beëindig mijn_clk_div;

Ons laatste onderdeel in dit diagram is een gedragsmatig VHDL-bronbestand met voorwaarden voor de uitgangen op basis van de configuratie van ingangssignalen.

Stap 3: D-teenslippers

De vier flip-flops die aan de ingangssignalen zijn bevestigd, zijn essentieel voor de functionaliteit van ons systeem. Zoals eerder gezegd, met gevoelige bewegingssensoren en een override-knop, gebruiken de flip-flops vergrendelingen om ons ingangssignaal alleen uit te voeren op de stijgende flank van de klok. Deze sequentiële logica betekent dat onze straatlantaarns een bepaalde tijd aan kunnen blijven nadat ze zijn geactiveerd door een snelle beweging. De codering voor een D-Flip Flop is vrij eenvoudig:

beginproces (CLK) begint als stijgende_rand (CLK) dan Q <= D; stop als; eindproces;

Het hele ding kan worden gecompileerd in een enkele if-statement. Toen we dit stuk eenmaal hadden, hebben we een structureel VHDL-bronbestand gemaakt met alle vier onze benodigde flip-flops:

begin DFF0: DFF-poortkaart (CLK => CLK, D => D(0), Q => Q(0)); DFF1: DFF-poortkaart (CLK => CLK, D => D(1), Q => Q(1)); DFF2: DFF-poortkaart (CLK => CLK, D => D (2), Q => Q (2)); DFF3: DFF-poortkaart (CLK => CLK, D => D (3), Q => Q (3));

einde Gedrags;

Dit helpt ons om ons structurele hoofdbestand, waarin we alle systeemcomponenten samenbrengen, veel overzichtelijker en overzichtelijker te houden.

Stap 4: Voorwaardelijke

Om onze code compact en efficiënt te houden, hebben we al onze conditionals in één case-statement geschreven. Voor ons verkleinde model hadden we 16 mogelijke LED-uitgangsconfiguraties, aangezien elke bewegingssensor verantwoordelijk is voor een groep van 4 LED's.:

geval NMS is wanneer "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "111111111111111"; eindgeval;

Stap 5: Beperkingen

Om uw invoer en uitvoer correct te vermelden met behulp van Vivado, moet u een beperkingsbestand implementeren met alle poorten, knoppen, LED's en klokken die worden gebruikt.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[0]}] set_property PACKAGE_PIN E19 [get_ports {LED[1]}] set_property IOSTANDARD LVCMOS33 [get_ports set_{100}{101} U19 [get_ports {LED[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[2]}] set_property PACKAGE_PIN V19 [get_ports {LED[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[3]}] set_property W18 [get_ports {LED[3]}] get_ports {LED[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[4]}] set_property PACKAGE_PIN U15 [get_ports {LED[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[5]}] set_property PACKAGE_PINTE LED[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[6]}] set_property PACKAGE_PIN V14 [get_ports {LED[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[7]}] set_property PACKAGE_PIN V13 [get 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[8]}] set_property PACKAGE_PIN V3 [get_ports {LED[9]}] set_property IO STANDARD LVCMOS33 [get_ports {LED[9]}] set_property PACKAGE_PIN W3 [get_ports {LED[10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[10]}] set_property PACKAGE_PIN U3 [get_ports {STANDARD_propertyCM}] set [get_ports {LED[11]}] set_property PACKAGE_PIN P3 [get_ports {LED[12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[12]}] set_property PACKAGE_PIN N3 [get_ports {LED[13]}] set_property IOSTANDARD {LED[13]}] set_property PACKAGE_PIN P1 [get_ports {LED[14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[14]}] set_property PACKAGE_PIN L1 [get_ports {LED[15]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED[14]}] [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS[0]}] set_property PACKAGE_PIN A16 [get_ports {MS[1]}] set_property IOSTANDARD LVCMOS33 [get_ports set_{100}{101} B15 [get_ports {MS[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS[2]}] set_property PACKAGE_PIN B16 [get_ports {MS[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS[3]}]

Stap 6: Hoofdbronbestand

In dit hoofdbestand brengen we alle eerder genoemde componentbronbestanden samen. Dit bestand fungeert als structurele code die de verschillende componenten samenbrengt.

entiteit Master_Final_Project is Port (BTN: in STD_LOGIC; CLK: in STD_LOGIC; MS: in STD_LOGIC_VECTOR (3 omlaag naar 0); LED: uit STD_LOGIC_VECTOR (15 omlaag naar 0)); einde Master_Final_Project;

architectuur Gedrag van Master_Final_Project is

component final_project is Port (--CLK: in STD_LOGIC; NMS: in STD_LOGIC_VECTOR (3 tot 0); BTN: in STD_LOGIC; --sw: in STD_LOGIC_Vector (1 tot 0); LED: uit STD_LOGIC_VECTOR (15 tot 0)); eindcomponent;

component Final_DFF is

Poort (CLK: in STD_LOGIC; D: in STD_LOGIC_Vector (3 omlaag naar 0); Q: uit STD_LOGIC_Vector (3 omlaag naar 0)); eindcomponent;

signaal DFF02proj30: STD_LOGIC;

signaal DFF12proj74: STD_LOGIC; signaal DFF22proj118: STD_LOGIC; signaal DFF32proj1512: STD_LOGIC;

beginnen

DFF0: Final_DFF poortkaart (CLK => CLK, D(0) => MS(0), D(1) => MS(1), D(2) => MS(2), D(3) => MS(3), Q(0) => DFF02proj30, Q(1) => DFF12proj74, Q(2) => DFF22proj118, Q(3) => DFF32proj1512); Proj0: final_project poortkaart (NMS(0) => DFF02proj30, NMS(1) => DFF12proj74, NMS(2) => DFF22proj118, NMS(3) => DFF32proj1512, BTN => BTN, LED => LED); einde Gedrags;

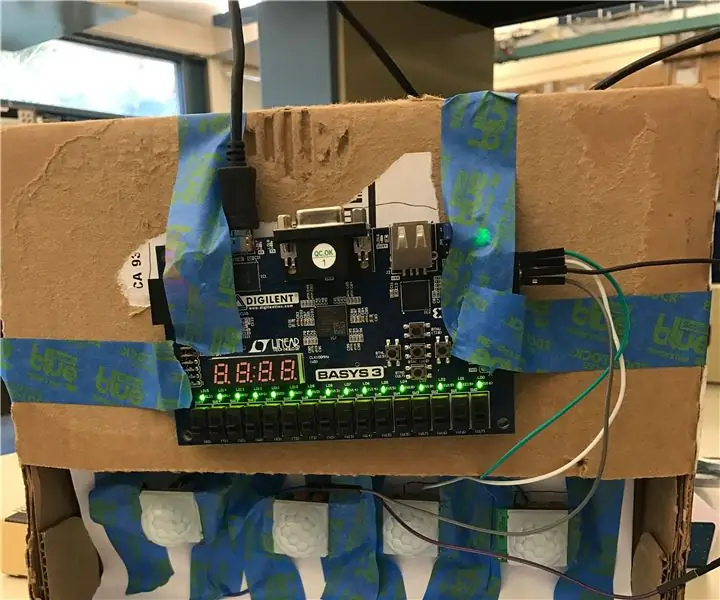

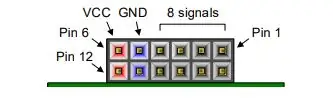

Stap 7: Montage

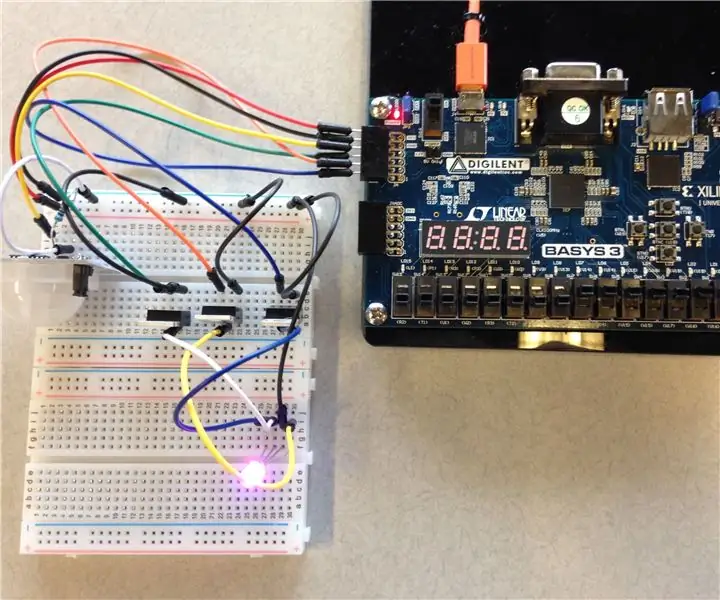

De hardware-assemblage voor dit project is minimaal. De enige vereiste stukken zijn als volgt:

1. Basys 3 bord (1)

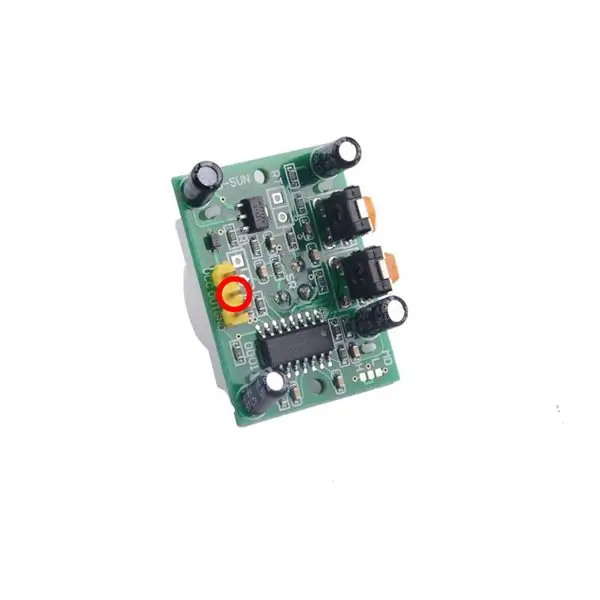

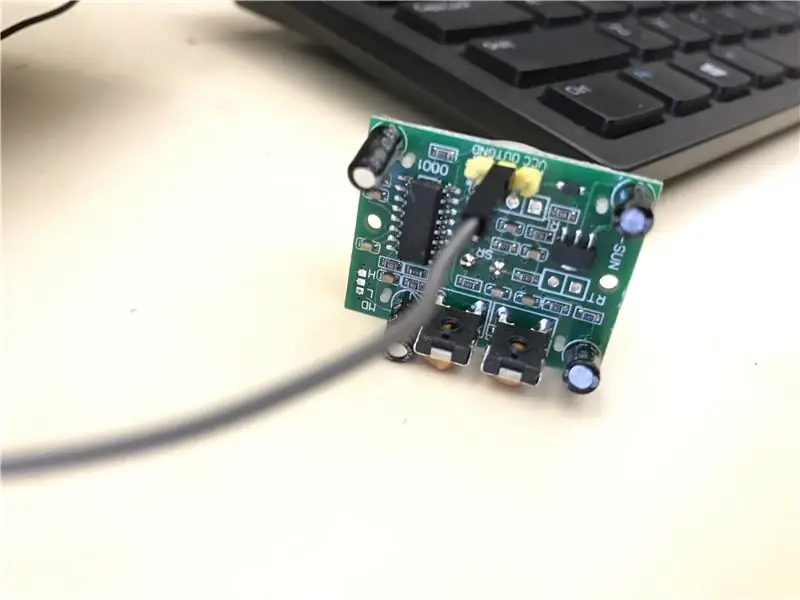

2. Goedkope bewegingssensoren die je hier op amazon kunt vinden. (4)

3. Man-naar-vrouw-leads (4)

Samenkomst:

1. Sluit 4 mannelijke draden aan op de JB-poorten 1-4 van de PMod-header (zie afbeelding).

2. Sluit de vrouwelijke uiteinden aan op de uitgangspin van elke bewegingssensor.

Stap 8: Het programma laden

Nu zijn we klaar om het VHDL-masterbronbestand naar het Basys 3-bord te laden. Zorg ervoor dat u de synthese, implementatie en het genereren van bitstreamcontrole op mogelijke fouten uitvoert. Als alles succesvol is uitgevoerd, opent u de hardwaremanager en programmeert u het Basys 3-apparaat. Uw project is nu voltooid!

Aanbevolen:

Door beweging geactiveerde cosplayvleugels met Circuit Playground Express - Deel 1: 7 stappen (met afbeeldingen)

Door beweging geactiveerde cosplayvleugels met Circuit Playground Express - Deel 1: Dit is deel één van een tweedelige project, waarin ik je mijn proces laat zien voor het maken van een paar geautomatiseerde feeënvleugels. Het eerste deel van het project is de mechanica van de vleugels, en het tweede deel is het draagbaar maken en de vleugels toevoegen

Door beweging geactiveerde lichten: 5 stappen

Door beweging geactiveerde lichten: deze gids laat u zien hoe u een FPGA kunt gebruiken om een door bewegingssensor geactiveerd licht van verschillende kleuren te creëren zolang er beweging is. De niveaus van rood, blauw en groen worden allemaal gecontroleerd door een waarde aan elke individuele kleur te koppelen. Dit project m

Sensorgebaseerde, door beweging geactiveerde muziekspeler: 3 stappen

Sensorgebaseerde, door beweging geactiveerde muziekspeler: op mijn bacheloropleiding moesten we een origineel project maken dat alle studenten zelf konden kiezen. Voor mijn project, aangezien ik altijd naar muziek luister en ik altijd het gevoel heb dat het te veel gedoe is om een luidspreker aan te zetten die ik

Door licht geactiveerde knipperende LED's: 4 stappen

Door licht geactiveerde knipperende LED's: in deze Instructable laat ik je zien hoe je een knipperend LED-circuit samenstelt dat aangaat wanneer je er met je hand overheen zwaait, een seconde of twee knippert en dan uitdooft. Ik heb het schema voor het knipperende circuit van de instructie van steven123654

Door beweging geactiveerde Spy Cam: 5 stappen (met afbeeldingen)

Motion Triggered Spy Cam: Nu kunt u geheime bewaking uitvoeren met deze "betrapt-in-beweging" spionage-videocamera die geheime video en audio opneemt. Zie het in actie en de testresultaten