Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:15.

- Laatst gewijzigd 2025-01-23 15:01.

Verbind je Mojo ontwikkelbord met externe inputs met dit shield.

Wat is het Mojo-ontwikkelbord?

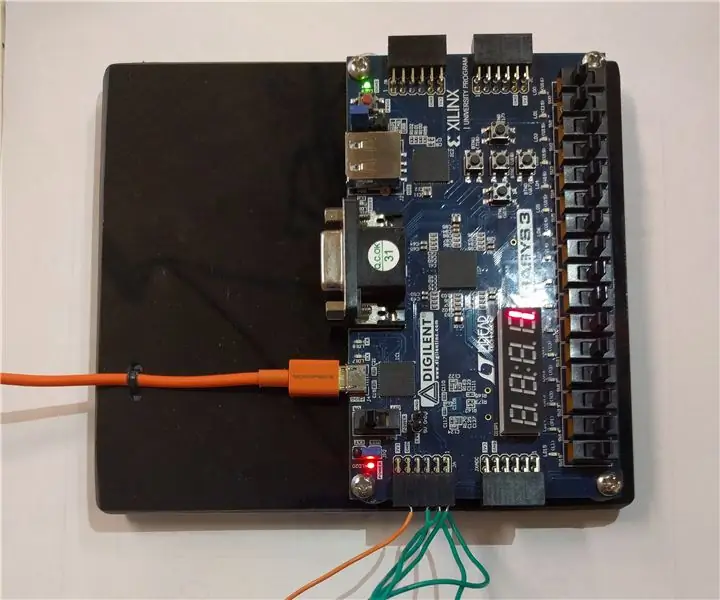

Het Mojo ontwikkelbord is een ontwikkelbord gebaseerd op de Xilinx Spartan 3 FPGA. Het bord is gemaakt door Alchitry. FPGA's zijn erg handig als er meerdere processen tegelijk moeten worden uitgevoerd.

Wat heb je nodig?

Benodigdheden

Mojo ontwikkelbord

Gerber-bestand

8 x 15k ohm weerstanden (optioneel*)

4 x 470 ohm weerstanden

4 x 560 ohm weerstanden

4 x CC zevensegmentendisplays

4 x 3 mm LED's

4 x SPDT tactiele schakelaars

1 x 4 standen DIP-schakelaar voor opbouwmontage

2 x 25 bij 2 of 4 x 25 kopteksten

1x 2 bij 5 pins dooskop

Soldeerbout

Soldeer

flux

*(als deze weerstanden worden weggelaten, moet interne pullup/pulldown worden ingeschakeld voor relevante pinnen)

Stap 1: Upload Gerber naar PCB-fabrikant van uw keuze

Voor mijn boards heb ik besteld bij JLC PCB.

De enige verandering die ik maakte was de kleur die ik wilde matchen met het zwart van de Mojo.

Stap 2: Bordmontage

Bij het solderen vind ik het altijd handig om eerst de onderste delen te solderen dus beginnen met de weerstanden is een goed idee.

R5, R6, R7, R8, R9, R10, R11 en R12 zijn weerstanden van 15k ohm die worden gebruikt om de schakelaars naar beneden te trekken (als je interne pullup/pulldown gebruikt, negeer dit dan).

R1, R2, R3, R4 zijn weerstanden van 560 ohm die verantwoordelijk zijn voor het beperken van de stroom door het 7-segments display.

R13, R14, R15, R16 zijn weerstanden van 470 ohm die verantwoordelijk zijn voor het beperken van de stroom door de 4 LED's.

Soldeer vervolgens de DIP-schakelaar, tactiele schakelaars, LED's, zeven segment displays en box header connector in die volgorde.

Plaats nu de 25 bij 2 (of 2 25 bij 1) in de mojo om de pinnen uit te lijnen. Lijn het schild uit met de pinnen en soldeer het op zijn plaats.

Stap 3: Software-installatie

Voor software verwijzend naar de website van Alchitry zal u laten weten wat u nodig heeft om aan de slag te gaan en de Xilinx ISE te installeren. Het wijzigen van het.ucf-bestand zodat het weet met welke pinnen is verbonden, is echter belangrijk om uw programma te laten werken.

Hier is het.ucf-bestand dat ik gebruik met het schild:

CONFIG VCCAUX=3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIODE "clk" 50 MHz HOOG 50%; NET "clk" LOC = P56 | IOSTANDAARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDAARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDAARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDAARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDAARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDAARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDAARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDAARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDAARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDAARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDAARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDAARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDAARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDAARD = LVTTL; NET "Q[0]" LOC = P26 | IOSTANDAARD = LVTTL; NET "Q[1]" LOC = P23 | IOSTANDAARD = LVTTL; NET "Q[2]" LOC = P21 | IOSTANDAARD = LVTTL; NET "Q[3]" LOC = P16 | IOSTANDAARD = LVTTL; NET "S[0]" LOC = P7 | IOSTANDAARD = LVTTL; NET "S[1]" LOC = P9 | IOSTANDAARD = LVTTL; NET "S[2]" LOC = P11 | IOSTANDAARD = LVTTL; NET "S[3]" LOC = P14 | IOSTANDAARD = LVTTL; NET "pb[1]" LOC = P30 | IOSTANDAARD = LVTTL; NET "pb[2]" LOC = P27 | IOSTANDAARD = LVTTL; NET "pb[3]" LOC = P24 | IOSTANDAARD = LVTTL; NET "pb[4]" LOC = P22 | IOSTANDAARD = LVTTL; NET "sevsega[0]" LOC = P57 | IOSTANDAARD = LVTTL; NET "sevsegb[0]" LOC = P58 | IOSTANDAARD = LVTTL; NET "sevsegc[0]" LOC = P66 | IOSTANDAARD = LVTTL; NET "sevsegd[0]" LOC = P67 | IOSTANDAARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDAARD = LVTTL; NET "sevsegf[0]" LOC = P75 | IOSTANDAARD = LVTTL; NET "sevsegg[0]" LOC = P78 | IOSTANDAARD = LVTTL; NET "sevsegdp[0]" LOC = P80 | IOSTANDAARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDAARD = LVTTL; NET "sevsegb[1]" LOC = P83 | IOSTANDAARD = LVTTL; NET "sevsegc[1]" LOC = P84 | IOSTANDAARD = LVTTL; NET "sevsegd[1]" LOC = P85 | IOSTANDAARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDAARD = LVTTL; NET "sevsegf[1]" LOC = P88 | IOSTANDAARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDAARD = LVTTL; NET "sevsegdp[1]" LOC = P94 | IOSTANDAARD = LVTTL; NET "sevsega[2]" LOC = P97 | IOSTANDAARD = LVTTL; NET "sevsegb[2]" LOC = P98 | IOSTANDAARD = LVTTL; NET "sevsegc[2]" LOC = P99 | IOSTANDAARD = LVTTL; NET "sevsegd[2]" LOC = P100 | IOSTANDAARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDAARD = LVTTL; NET "sevsegf[2]" LOC = P102 | IOSTANDAARD = LVTTL; NET "sevsegg[2]" LOC = P104 | IOSTANDAARD = LVTTL; NET "sevsegdp[2]" LOC = P111 | IOSTANDAARD = LVTTL; NET "sevsega[3]" LOC = P114 | IOSTANDAARD = LVTTL; NET "sevsegb[3]" LOC = P115 | IOSTANDAARD = LVTTL; NET "sevsegc[3]" LOC = P116 | IOSTANDAARD = LVTTL; NET "sevsegd[3]" LOC = P117 | IOSTANDAARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDAARD = LVTTL; NET "sevsegf[3]" LOC = P119 | IOSTANDAARD = LVTTL; NET "sevsegg[3]" LOC = P1120 | IOSTANDAARD = LVTTL; NET "sevsegdp[3]" LOC = P121 | IOSTANDAARD = LVTTL;

Onthoud dat als je de pulldown-weerstanden niet hebt geïnstalleerd om de pinnen in de.ucf te bewerken met

| OMLAAG TREKKEN; O

| OPTREKKEN;

Als je het blok ergens voor wilt gebruiken, zijn de verbindingen als volgt. Links is het blokpinnummer en rechts is het mojo-pinnummer dat u in uw.ucf moet toewijzen:

pin 1 = 29

pin 2 = 51

pin 3 = 32

pin 4 = 41

pin 5 = 34

pin 6 = 35

pin 7 = 40

pin 8 = 33

pin 9 = GND

pin 10 = +V

Aanbevolen:

Maak elke sensor uit een FPGA: 4 stappen

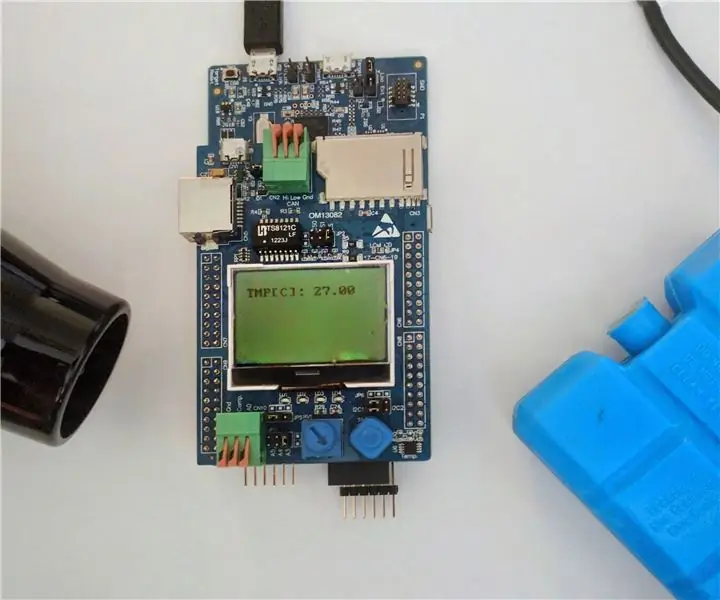

Maak elke sensor uit een FPGA: de meeste makers hebben minstens één keer in hun leven geprobeerd een thermometer te bouwen, misschien is degene die ze thuis hebben niet slim genoeg, of misschien denken ze dat ze het volgende NEST kunnen bouwen. Niettemin hadden ze op een gegeven moment een microcontroller met hun status

JALPIC One Development Board: 5 stappen (met afbeeldingen)

JALPIC One Development Board: Als je mijn Instructables-projecten volgt, weet je dat ik een grote fan ben van de JAL-programmeertaal in combinatie met de PIC Microcontroller. JAL is een Pascal-achtige programmeertaal die is ontwikkeld voor de 8-bit PIC-microcontrollers van Microchip. Mo

FPGA-reactiespel: 10 stappen

FPGA-reactiespel: tegen de zomer Rutherford en Regita Soetandar

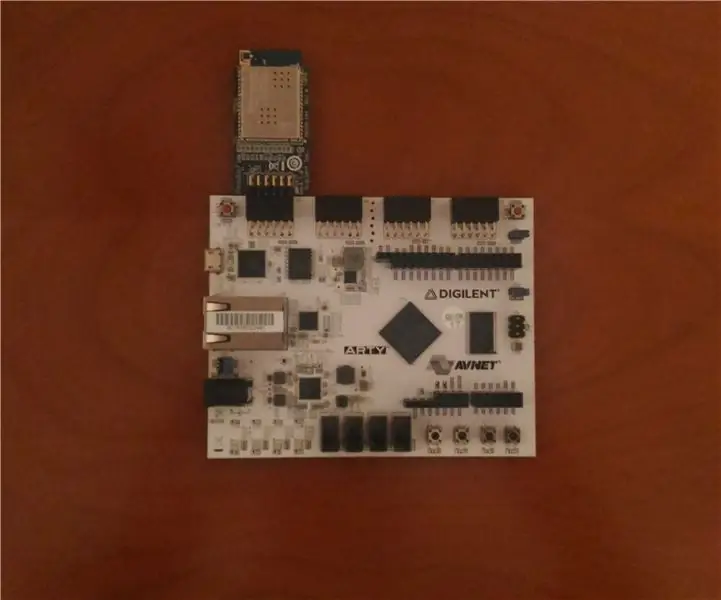

PmodWiFi FPGA-stuurprogramma: 9 stappen

PmodWiFi FPGA-stuurprogramma: dit is een Instructable voor diegenen die een Pmod WiFi willen gebruiken in combinatie met een FPGA-bord

De heer E.Z. Tube Development Board: 4 stappen (met afbeeldingen)

De heer E.Z. Tube Development Board: Doel/doel: Dhr. E.Z. Tube is een goedkoop vacuümbuis audioplatform zonder het 'ijzer': geen stroomtransformator, geen uitgangstransformator(en). Een buizenversterker heeft doorgaans meerdere zware, dure transformatoren: uitgangstransformatoren die luidsprekers beschermen