Inhoudsopgave:

- Stap 1: Blokdiagram

- Stap 2: Werkingsprincipe

- Stap 3: Logische implementatie

- Stap 4: Impasse oplossen

- Stap 5: Apparaatconfiguratie - Matrix0 Circuit

- Stap 6: Apparaatconfiguratie - SPI-kloklogica

- Stap 7: Apparaatconfiguratie - Eigenschappen Matrix0 Componenten

- Stap 8: Apparaatconfiguratie - Matrix1-circuit

- Stap 9: Apparaatconfiguratie - 3-bits binaire teller

- Stap 10: Apparaatconfiguratie - 3-bits vergelijkingslogica

- Stap 11: Apparaatconfiguratie - Digitale vergelijkingslogica en tijdelijk register

- Stap 12: Apparaatconfiguratie - Eigenschappen Matrix1 Componenten

- Stap 13: Resultaten

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:15.

- Laatst gewijzigd 2025-01-23 15:01.

Besturingssystemen en aanverwante apparaten hebben te maken met meerdere stroombronnen, zoals bias-lijnen of batterijen, en moeten de hoogste (of de laagste) lijn van een bepaalde set volgen.

Het schakelen van belasting in een systeem met meerdere batterijen vereist bijvoorbeeld dat het systeem de minimale of maximale spanning tussen de batterijreeks bewaakt (max of min als functie van het specifieke schakelalgoritme) en de belasting dynamisch naar de meest geschikte bron in realtime. Het kan ook zijn dat het systeem de batterij met de laagste spanning tijdelijk moet loskoppelen om correct op te laden.

Een ander voorbeeld is het moderne zonne-energiesysteem, waarbij elk zonnepaneel is uitgerust met een kantelmechanisme en met een zonnevolgcircuit (de laatste levert de zonpositie-informatie om het paneel te oriënteren). Met de max-voltage-info kan elke positie van het zonnepaneel nauwkeurig worden afgesteld op basis van het paneel van de string dat daadwerkelijk de hoogste uitgangsspanning levert, waardoor een superieur niveau van vermogensoptimalisatie wordt bereikt.

Er zijn verschillende merken commerciële IC's (voornamelijk microcontrollers) die in principe een max-spanningsvolger kunnen implementeren. Ze vereisen echter programmering en zijn minder kosteneffectief dan een mixed-signal oplossing. Het aanvullen van een Dialog GreenPAKTM-ontwerp kan een positieve invloed hebben op de betaalbaarheid, omvang en modulariteit van het ontwerp. Dit ontwerp maakt gebruik van het voordeel van de integratie van zowel analoge als digitale circuits in één enkele chip.

In deze Instructable zijn de analoge front-end en de digitale logica die nodig is om een max (of uiteindelijk min) spanningzoeker tussen acht verschillende bronnen te implementeren, geïmplementeerd.

Om de 8-kanaals analoge max/min spanningsmonitor te implementeren wordt een SLG46620G gebruikt.

Hieronder hebben we de stappen beschreven die nodig zijn om te begrijpen hoe de oplossing is geprogrammeerd om de 8-kanaals analoge max/min-spanningsmonitor te creëren. Als u echter alleen het resultaat van het programmeren wilt hebben, download dan GreenPAK-software om het reeds voltooide GreenPAK-ontwerpbestand te bekijken. Sluit de GreenPAK Development Kit aan op uw computer en druk op programma om de 8-kanaals analoge max/min-spanningsmonitor te maken.

Stap 1: Blokdiagram

De figuur 1 toont het globale diagram van het geïmplementeerde systeem.

Een reeks van maximaal 8 variabele spanningsbronnen is gemultiplext en gekoppeld aan een ADC-module van een GreenPAK die is aangesloten op een aangepast intern ontwerp dat in staat is om de bron met de hoogste spanning te selecteren ten opzichte van de andere. De interne logica geeft deze informatie weer voor weergave of verdere verwerking.

Het ontwerp is gebaseerd op het product GreenPAK SLG46620G, omdat het alle benodigde analoge en digitale bouwstenen voor de toepassing bevat. In deze implementatie wordt de array gescand door middel van een ADG508 analoge multiplexer die direct wordt aangestuurd door de GreenPAK IC.

De uitgangsinformatie is een 3-bit digitaal getal dat overeenkomt met het spanningsbronnummer bij maximale spanning. Een directe manier om deze informatie te krijgen is door het nummer weer te geven door middel van een 7-segments display. Dit kan eenvoudig worden bereikt door de digitale uitgang van de SLG46620G te koppelen aan een 7-segments displaydriver, zoals de GreenPAK-oplossing die wordt beschreven in Reference of aan een gewone 74LS47 IC.

Het gepresenteerde circuit zoekt naar maximale spanning. Om het ontwerp om te zetten in een minimumspanningszoeker, moet een eenvoudig pre-conditioneringscircuit worden toegevoegd tussen de analoge multiplexer en de GreenPAK analoge ingang, waarbij de multiplexeruitgang wordt afgetrokken van een referentiespanning van 1 V.

Stap 2: Werkingsprincipe

Het ontwerp is bedoeld om de bron met maximale spanning te selecteren, daarom wordt een scan uitgevoerd op de hele array terwijl de laatste-max-waarde wordt opgeslagen en deze wordt vergeleken met de volgende waarde in de invoer (die bij de volgende spanningsbron in de scan hoort).

In het volgende zullen we naar een volledige multiplexreeks langs alle ingangen verwijzen als een "scan" of "loop".

Vergelijking tussen twee waarden wordt niet bereikt door middel van ACMP-componenten (echter beschikbaar in de SLG46620G), maar eerder door de DCMP-module, zodra de waarden respectievelijk zijn gedigitaliseerd. Dit is een geavanceerde en verfijnde techniek die voor het eerst wordt behandeld in Reference.

Afbeelding 2 laat zien hoe de SLG46620G is gestructureerd voor dit ontwerp.

Het analoge ingangssignaal gaat naar de ADC-ingang via de PGA-component met een ingestelde Gain van 1. Er zijn ook verschillende Gain-instellingen mogelijk om de beste match te vinden met de front-end conditioneringselektronica die is gewijd aan het in kaart brengen van de ingangsspanningen naar de 0-1 V bereik van de GreenPAK ADC-module.

De ADC werkt in single-ended modus en zet het analoge signaal om in een 8-bits digitale code, die vervolgens wordt overgebracht naar de DCMP-module. De digitale code wordt ook ingevoerd in het SPI-blok, geconfigureerd als een ADC/FSM-buffer, waar een digitale code kan worden opgeslagen en niet verandert totdat de volgende puls op de SPI CLK-ingang komt. Merk op dat een speciaal logisch blok de SPI CLK-ingang aandrijft. We zullen dit deel later onderzoeken, omdat dit de "kern" -logica is die verantwoordelijk is voor een goede werking. Een nieuwe digitale code wordt alleen in de SPI-module opgeslagen als deze bij de werkelijke maximale ingangsspanning hoort.

De DCMP-component wordt gebruikt om de huidige ADC-gegevens te vergelijken met de laatste winnaar (dat is de laatst gevonden max) die is opgeslagen in het SPI-blok. Het genereert een puls aan de OUT+-uitgang wanneer nieuwe ADC-gegevens groter zijn dan de vorige. We gebruiken het OUT+-signaal om het SPI-blok bij te werken met de nieuwe winnaar.

Een globaal kloksignaal stuurt ADC-conversies en algemene timings aan. Zodra een conversie is uitgevoerd, pulseert het INT-uitgangssignaal van de ADC, gecoördineerd in de tijd met de parallelle data-uitgang van de ADC. We gebruiken de INT-uitvoer ook om een 3-bits binaire teller te verhogen, geïmplementeerd door DFF's in Matrix1, wat om drie redenen nuttig is:

1. De telleruitgangslijnen adresseren de externe analoge multiplexer en bedienen zo de volgende ingangsspanning naar de ADC;

2. De telling wordt bevroren in een 3-bits register (geïmplementeerd in Matrix1) om de tijdelijke winnaar tijdens een scan op te slaan;

3. De telling wordt gedecodeerd om een tweede 3-bits register bij te werken (geïmplementeerd in Matrix0) zodra een scan is voltooid.

Stap 3: Logische implementatie

De ADC-module levert sequentieel geconverteerde gegevens van alle ingangsspanningen, de een na de ander, voor onbepaalde tijd. Zodra de multiplexer is geadresseerd 0b111 (decimaal 7), loopt de teller terug naar 0b000 (decimaal 0), waardoor een nieuwe scan van de ingangsspanningen wordt gestart.

Tijdens de scan wordt het ADC INT-uitgangssignaal gegenereerd wanneer de parallelle gegevensuitgang geldig is. Wanneer dit signaal pulseert, moet de analoge multiplexer overschakelen naar de volgende ingang, waardoor de PGA de bijbehorende spanning krijgt. Daarom is de ADC INT-uitgang het directe kloksignaal van de 3-bits binaire teller van figuur 2, waarvan het 3-bit parallelle uitgangswoord rechtstreeks de externe analoge multiplexer aanspreekt (“V select” in figuur 1).

Laten we nu verwijzen naar een voorbeeld waarin de ingangsspanningen verondersteld worden de volgende relaties te hebben:

a) V0 < V1 < V2

b) V2 > V3, V4

c) V5 > V2

Figuur 3 geeft de belangrijkste signalen weer die betrokken zijn bij het max-beslissingsmechanisme.

Aangezien gegevens uiteindelijk synchroon met INT-pulsen in het SPI-bufferregister worden geklokt, bestaat er een vergelijkingsvenster waarin de SPI-bufferinhoud wordt vergeleken met het volgende ADC-conversieresultaat. Deze specifieke timing resulteert in het genereren van OUT+-pulsen aan de DCMP-uitgang. We kunnen profiteren van deze pulsen om nieuwe waarden in het SPI-bufferregister te laden.

Zoals blijkt uit de SPI-buffergegevenslijn van de voorgaande afbeelding, bevat het SPI-register altijd, keer op keer, de grootste waarde van de 8 ingangen en wordt het alleen bijgewerkt wanneer een grotere waarde wordt gedetecteerd door de DCMP-module (verwijzend naar de DCMP OUT+ uitgangslijn van de plot, zorgen de ontbrekende pulsen ervoor dat V2 vergrendeld blijft in het register tot vergeleken met V5).

Stap 4: Impasse oplossen

Als de geïmplementeerde logica zou zijn zoals hierboven beschreven, is het duidelijk dat we tegen een impasse zouden aanlopen: het systeem is in staat om alleen spanningen te detecteren die hoger zijn dan de spanning die overeenkomt met wat is opgeslagen in het SPI-bufferregister.

Dit geldt ook in het geval dat deze spanning zou afnemen en dan een andere ingang, tot nu toe lager dan die, de hoogste wordt: deze zou nooit worden gedetecteerd. Deze situatie wordt beter uitgelegd in figuur 4 waar slechts 3 ingangsspanningen aanwezig zijn omwille van helderheid.

Op het moment van iteratie 2 daalt V3 en is V1 de werkelijke maximale spanning. Maar de DCMP-module geeft geen puls omdat de gegevens die zijn opgeslagen in het SPI-bufferregister (overeenkomend met 0,6 V) groter zijn dan die van V1 (0,4 V).

Het systeem gedraagt zich dan als een "absolute" max-zoeker en werkt de uitvoer niet correct bij.

Een goede manier om dit probleem op te lossen, is door de gegevens geforceerd opnieuw te laden in het SPI-bufferregister wanneer het systeem een volledige pollingcyclus van alle kanalen voltooit.

Als de spanning op die ingang nog steeds de hoogste is, verandert er niets en gaat de besturing veilig door (verwijzend naar figuur 4 hierboven, dit is het geval voor lusiteraties 0 en 1). Aan de andere kant, als de spanning op die ingang per ongeluk daalt tot een waarde die lager is dan die van een andere ingang, dan geeft het herladen van de waarde de DCMP-module de mogelijkheid om een OUT+-puls te produceren wanneer deze wordt vergeleken met de nieuwe maximale waarde (dit is de geval van Loop Iteraties 2 en 3).

Een stukje logisch circuit is nodig om het probleem op te lossen. Het moet een kloksignaal naar de SPI-component genereren wanneer de lus de werkelijke maximale invoer bereikt, waardoor een herladen van het bijgewerkte datawoord in het SPI-bufferregister wordt geforceerd. Dit wordt besproken in de paragrafen 7.2 en 7.6 hieronder.

Stap 5: Apparaatconfiguratie - Matrix0 Circuit

De SLG46620G heeft twee Matrix-blokken, zoals afgebeeld in afbeelding 2. De volgende afbeeldingen tonen de respectievelijke apparaatconfiguraties.

Het bovenste gedeelte van het circuit is het "Loop Register" gerealiseerd met 3 DFF's (DFF0, DFF1 en DFF2). Het wordt ververst na elke lus van de ingangsmultiplexer om het binaire getal van de "winnaar", dat wil zeggen de ingang met de hoogste spanning in de laatste scan, naar een 7-segments display-stuurprogramma te sturen. Zowel de klok naar de DFF's als de gegevens komen van de logica die is geïmplementeerd in Matrix1 via respectievelijk poort P12, P13, P14 en P15.

Het onderste deel is de analoge front-end met ingang op Pin 8 en PGA met versterking x1. De ADC INT-uitgang gaat zowel naar de kloklogica van SPI als naar Matrix1 via poort P0, waar het zal dienen als het kloksignaal voor de geïmplementeerde teller.

ADC en SPI parallelle data-uitgangen zijn respectievelijk gelabeld als NET11 en NET15 om te worden aangesloten op de DCMP-component in Matrix1.

Stap 6: Apparaatconfiguratie - SPI-kloklogica

Zoals eerder aangegeven in de sectie "Logische implementatie", wordt het SPI-bufferregister bijgewerkt telkens wanneer een vergelijking tussen de werkelijke opgeslagen waarde en de nieuwe ADC-conversiegegevens een puls genereert op de DCMP OUT+-uitgang.

Signaalintegriteit is verzekerd als dit signaal wordt ge-AND-ed met de ADC INT-uitgang. Dit voorkomt pieken en valse triggers.

We hebben ook benadrukt dat om deadlock-situaties over te slaan, de SPI-buffer moet worden bijgewerkt wanneer de lus de daadwerkelijke winnaargegevens bereikt.

Er zijn dan drie signalen in het spel voor een juiste SPI-klokken:

1. ADC INT-uitgang (LUT0-IN1)

2. DCMP OUT+ uitgang (LUT0-IN0 via poort P10)

3. Telling is gelijk aan Latch-signaal (LUT0-IN2 via poort P11)

De eerste twee zijn AND-ed en beide OR-ed met de laatste in LUT0, waarvan de implementatie is geconfigureerd zoals in figuur 6.

Stap 7: Apparaatconfiguratie - Eigenschappen Matrix0 Componenten

De figuren 7-10 tonen de overige eigenschappenvensters van de componenten die bij Matrix0 horen.

Stap 8: Apparaatconfiguratie - Matrix1-circuit

Stap 9: Apparaatconfiguratie - 3-bits binaire teller

Het bovenste deel van de schakeling bevat logische elementen, voornamelijk een 3-bit binaire teller die wordt geklokt door de ADC INT-uitgang, zoals reeds besproken. Deze teller is geïmplementeerd met een vrij "standaard" schema dat wordt weergegeven in figuur 12.

Deze teller is in ons ontwerp gerealiseerd door middel van Flip-Flops DFF9, DFF10, DFF11 en INV1, LUT4, LUT8. De DFF9-uitgang is de LSB, terwijl DFF11 de MSB is, zoals weergegeven in afbeelding 13.

LUT4 is geconfigureerd als een XOR, terwijl LUT8 de AND-XOR-logica van Afbeelding 12 uitvoert.

Telleruitgangen gaan naar drie digitale uitgangspinnen om de externe analoge multiplexer te adresseren.

LUT10 decodeert de code van de teller wanneer een scan is voltooid en stuurt een puls naar Matrix0 via DLY8 en poort P12. Dit wordt eenvoudig bereikt door de uitgangen van de teller te EN-en, waardoor nummer 7 dec (0b111 binair, einde lus) wordt gedecodeerd.

Stap 10: Apparaatconfiguratie - 3-bits vergelijkingslogica

Afbeelding 15 toont het circuit dat wordt gebruikt om te detecteren wanneer de lus itereert op het huidige "winnaar" -adres. In dit geval, zoals reeds besproken, zou een digitale puls een herladen van het huidige ADC-resultaat moeten forceren om een mogelijke impasse op te lossen.

Het "winnaar"-adres wordt opgeslagen in het tijdelijke register van Matrix1 (zie hieronder), terwijl het huidige adres wordt uitgevoerd door de binaire teller.

XNOR-poorten bieden een echte (logische 1 of 'hoge') uitgang wanneer beide ingangen gelijk zijn. AND-ing dit signaal voor alle bits (LUT9) geeft ons een puls wanneer beide binaire codes hetzelfde zijn. Details over XOR-poorten als pariteitscontrole zijn te vinden in Reference.

Het signaal ‘Counter-equals-Latch’ wordt via poort P11 doorgegeven aan Matrix0.

Stap 11: Apparaatconfiguratie - Digitale vergelijkingslogica en tijdelijk register

Het onderste deel van figuur 11 (gemarkeerd in figuur 16) toont het DCMP-blok, het beslissingsdeel van dit ontwerp.

DFF6, 7 en 8 vormen een 3-bits register om het tijdelijke invoernummer "winnaar" op te slaan terwijl de lus loopt. Input voor de flip-flops zijn de 3-bits binaire telleruitgangen, zoals zichtbaar in het globale Matrix1-circuit van figuur 11, hier overgeslagen voor de duidelijkheid.

Uitgangen van dit register kunnen het 7-segmentsdisplay niet rechtstreeks aansturen omdat de hier opgeslagen waarde tijdens een scan verandert en pas aan het einde van de scan zelf als 'geldig' moet worden beschouwd.

Om deze reden worden de tijdelijke registeruitgangen aangesloten op het lusregister van de Matrix0 via inter-matrixpoorten P13, P14 en P15.

Het is belangrijk om op te merken in Afbeelding 16 dat het tijdelijke register wordt geklokt door de DCMP OUT+-uitgang wanneer de ADC-SPI-registersvergelijkingsresultaten resulteren in een nieuw gevonden maximum.

Hetzelfde OUT+ signaal wordt doorgegeven aan Matrix0, SPI CLK Logic, via poort P10.

Stap 12: Apparaatconfiguratie - Eigenschappen Matrix1 Componenten

De figuren 17-19 tonen de eigenschappenvensters van de componenten die bij Matrix1 horen.

Stap 13: Resultaten

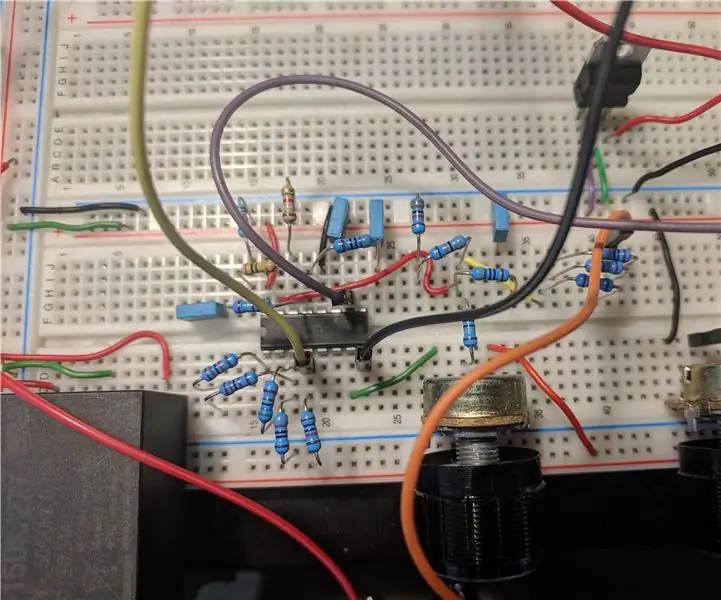

Om de implementatie te testen, is een prototype van een evaluatiebord geconstrueerd, waarbij de 8 analoge ingangsspanningen worden verkregen door een reeks weerstandsdelers met TrimPots (zoals weergegeven in Afbeelding 20).

De gebruikte multiplexer is een ADG508, een onderdeel dat kan werken met enkelvoudige voeding (12 V).

De driver met 7 segmenten is een 74LS47. Het decodeert een parallel ingangswoord en stuurt rechtstreeks een 7-segments display met gemeenschappelijke anode aan.

Het evaluatiebord heeft een 2x10 haakse connector die rechtstreeks kan worden aangesloten op een GreenPAK Advanced Development Platform via de uitbreidingsconnector, zoals weergegeven in afbeelding 21.

De combinatie met het GreenPAK Advanced Development Platform maakt het zeer eenvoudig om de signalen te meten voor een snelle controle. Afbeelding 22 toont bijvoorbeeld een reeks signalen (respectievelijk CLOCK, ADC INT-uitvoer en DCMP OUT+-uitvoer) zoals vastgelegd door een HP 54620A Logic Analyzer. Golfvormen worden geactiveerd door een stijgende flank van het OUT+-signaal (op de scoop aangeduid als 'A>B'), vandaar dat dit een golfvormregistratie is wanneer een nieuwe max. Spanning wordt gedetecteerd tussen de analoge ingangen. In feite werd het verkregen door een van de TrimPots van het evaluatiebord te draaien om de overeenkomstige spanning zoals weergegeven in afbeelding 22 te verhogen.

Figuur 23 toont het schema van de Evaluation Board.

Conclusie

In deze Instructable hebben we een achtkanaals max (of min) spanningszoeker geïmplementeerd die kan worden gebruikt als een algemene toevoeging aan meerkanaals besturingssystemen. De gepresenteerde benadering maakt gebruik van geavanceerde functies van de GreenPAK-componenten en laat zien hoe het mogelijk is om analoge en digitale functies in één chip te integreren. Verschillende commerciële IC's kunnen worden vervangen door Dialog GreenPAK's, zodat de omvang van de toepassing en de kosten kunnen worden verminderd.

Aanbevolen:

Analoge joystick #HMS2018: 8 stappen

Analoge joystick # HMS2018: je hebt één Elegoo Uno R3 adruino, één Elegoo-joystickmodule en 5 vrouwelijke naar mannelijke DuPoint-draden nodig

ANALOGE ULTRASONE SENSOR voor AFSTANDSMETING: 3 stappen

ANALOGE ULTRASONE SENSOR voor AFSTANDSMETING: Deze instructables gaan over het gebruik van een ultrasone sensor die op Arduino is aangesloten en om nauwkeurig afstanden van 20 cm tot 720 cm te meten

Verbeterde halfgeleidercurve-tracer met de analoge ontdekking 2: 8 stappen

Verbeterde Semiconductor Curve Tracer met de Analog Discovery 2: Het principe van curve tracing met de AD2 wordt beschreven in de volgende links hieronder: https://www.instructables.com/id/Semiconductor-Cur… https://reference.digilentinc .com/reference/instru…Als de gemeten stroom vrij hoog is, is de accu

Analoge metingen uitvoeren op de Raspberry Pi: 5 stappen

Analoge metingen uitvoeren op de Raspberry Pi: Hallo allemaal! In deze tutorial laat ik je zien hoe we direct analoge waarden kunnen vastleggen met behulp van de Raspberry Pi. Zoals we allemaal weten, is de Raspberry Pi een behoorlijk krachtige minicomputermodule die populair is bij hobbyisten en professionele

Laten we bouwen (analoge synth): 5 stappen

Let's Build (Analogue Synth): In deze serie laat ik je zien hoe je een eenvoudige modulaire analoge synthesizer bouwt met zowel analoge als digitale componenten.Link naar schema en componenten: https://drive.google.com/open?id= 1mZX4LyiJwXZLJ3R56SDxloMnk8z07IYJ