Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:15.

- Laatst gewijzigd 2025-01-23 15:01.

Door AmCoderhttps://www.linkedin.com/in/mituVolg meer door de auteur:

Over: Mitu Raj -- Gewoon een hobbyist en leerling -- Chipontwerper -- Softwareontwikkelaar -- Natuur- en wiskundeliefhebber Meer over AmCoder »

##Dit is de meest aangeklikte, populaire link in Google voor VHDL-implementatie van CORDIC ALGORITHM om sinus- en cosinusgolven te genereren## Op dit moment bestaan er veel hardware-efficiënte algoritmen, maar deze zijn niet goed bekend vanwege de dominantie van softwaresystemen over de vele jaren. CORDIC is zo'n algoritme dat niets anders is dan een reeks verschuivings- en add-logica's die worden gebruikt voor het berekenen van een breed scala aan functies, waaronder bepaalde trigonometrische, hyperbolische, lineaire en logaritmische functies. Dit is het algoritme dat wordt gebruikt in rekenmachines enz. Dus door alleen eenvoudige shifters en adders te gebruiken, kunnen we een hardware ontwerpen met minder complexiteit maar met de kracht van DSP met behulp van een cordic-algoritme. Daarom kan het worden ontworpen als kaal RTL-ontwerp in VHDL of Verilog zonder speciale drijvende-komma-eenheden of complexe wiskundige IP's te gebruiken.

Stap 1: VHDL en Modelsim

Hier wordt het cordic-algoritme geïmplementeerd met behulp van VHDL om een sinusgolf en cose-golf te genereren. Het kan sinus en cosinus van invoerhoek met grote precisie uitvoeren. De code is synthetiseerbaar op FPGA. Modelsim wordt gebruikt om het ontwerp en de testbank te simuleren.

Stap 2: VHDL-code voor het ontwerp en de testbank

Binaire schaaltechniek wordt gebruikt om getallen met drijvende komma weer te geven.

Ga door de bijgevoegde documenten voordat u codeert.

Ga doorSimuleren cordic_v4.vhd - Het ontwerp - De invoer is een hoek in 32 bits + tekenbit; het kan elke hoek van 0 tot +/- 360 graden verwerken met een invoerprecisie van 0.000000000233 graden. Bij het geven van invoer -> MSB is het tekenbit en de rest 32 bits vertegenwoordigen magnitude.-De uitvoer van het ontwerp is de sinus- en cos-waarde in 16 bits + tekenbit.ie; met precisie 0,00001526. Houd er rekening mee dat de uitvoer wordt weergegeven in de vorm van een 2 als de respectieve sinus- of cos-waarde negatief is. Simuleren testb.vhd - Testbank voor het ontwerp (1) Invoerhoeken en pull-reset ='0'. Trek na twee simulatiestappen terug naar '1' en "alles uitvoeren". (2) Stel in het simulatievenster de radix van sin en cos-signalen in als decimaal en formaat> Analoog (automatisch). (3) Zoom uit om de golfvorm te zien naar behoren.

Stap 3: Bijgevoegde bestanden

(1) cordic_v4.vhd - Ontwerp.(2) testb.vhd - Testbank voor het ontwerp.

(3) Documenteer hoe u hoekinvoer forceert en de binaire resultaten converteert.

Update: DEZE BESTANDEN ZIJN OBSELETE EN NIET MEER GELEVERD. GEBRUIK DE BESTANDEN VAN DE VOLGENDE STAP

Stap 4: Mini-Cordic IP-kern - 16 bit

Beperking van de bovenstaande implementatie is- langzame, lagere klokfrequentie vanwege het doen van berekeningen in een enkele klokcyclus. Mini-Cordic IP Core - 16 Bit

- Kritieke paden verdeeld over meerdere cycli om de prestaties te verbeteren. - Sneller - FPGA bewezen ontwerp gesynthetiseerd tot 100 Mhz klok. - Meer gebied geoptimaliseerd in HDL, minder hardware. - Load and Done Status-signalen toegevoegd.- Enige nadeel is een lagere resolutie vergeleken met de vorige. Testbench:

volledig geautomatiseerd van 0 tot 360 graden hoekinvoer

Bijgevoegde bestanden:1) mini cordic belangrijkste vhdl-bestand2) mini cordic testbank3) Mini Cordic IP Core handleiding4) Doc over hoe hoeken te forceren en resultaten om te zetten

Voor vragen kunt u gerust contact met mij opnemen:

Mitu Raj

volg mij:

mail: iammituraj@gmail.com

###Totaal aantal downloads: 325 tot 01-05-2021###

### Code laatst aangepast: juli-07-2020 ###

Aanbevolen:

PID-regelaar VHDL: 10 stappen

PID-controller VHDL: Dit project was mijn laatste project om mijn Honours Bachelor Degree van het Cork Institute of Technology af te ronden. Deze zelfstudie is opgedeeld in twee secties, de eerste behandelt het hoofdgedeelte van de PID-code, het hoofddoel van het project en de sec

Ontwerp van UART in VHDL: 5 stappen

Ontwerp van UART in VHDL: UART staat voor Universal Asynchronous Receiver Transmitter. Het is het meest populaire en eenvoudigste seriële communicatieprotocol. In deze instructable leert u hoe u een UART-module in VHDL ontwerpt

Mastermind-spel in VHDL: 3 stappen

Mastermind Game in VHDL: Voor ons project hebben we de “Mastermind” spel in VHDL om te spelen op het Basys3-bord. Mastermind is een codebrekend spel dat traditioneel gespeeld wordt met pinnen en een spelbord. Speler één plaatst pinnen van verschillende kleuren in een rij van 4

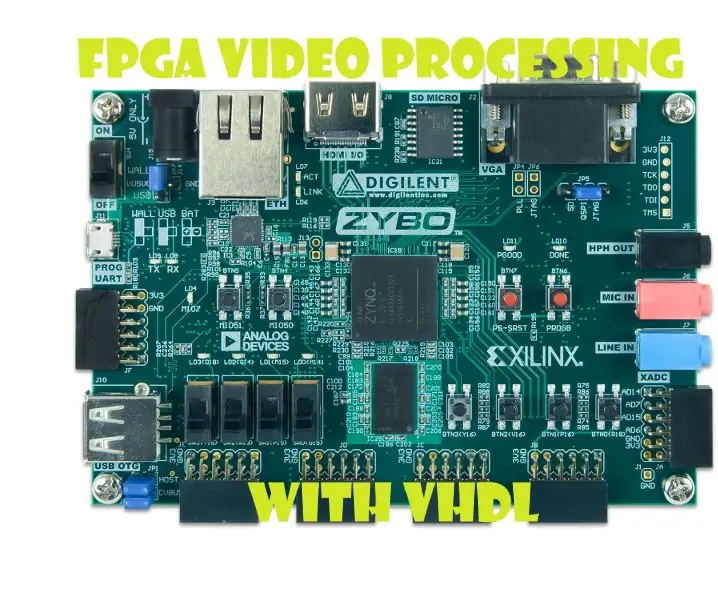

Videoverwerking met VHDL en een Zybo: 10 stappen

Videoverwerking met VHDL en een Zybo: FPGA's zijn sneller te verwerken dan CPU's, omdat ze veel parallel kunnen rekenen. Opmerking: dit project is nog in aanbouw en zal worden verbeterd (zodra ik tijd heb). Ondertussen reis ik de wereld rond

VHDL-stopwatch: 8 stappen (met afbeeldingen)

VHDL-stopwatch: dit is een tutorial over het maken van een stopwatch met VHDL en een FPGA-printplaat, zoals een Basys3 Atrix-7-bord. De stopwatch kan tellen van 00.00 seconden tot 99,99 seconden. Het maakt gebruik van twee knoppen, één voor de start/stop-knop en een andere voor de