Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:18.

- Laatst gewijzigd 2025-01-23 15:01.

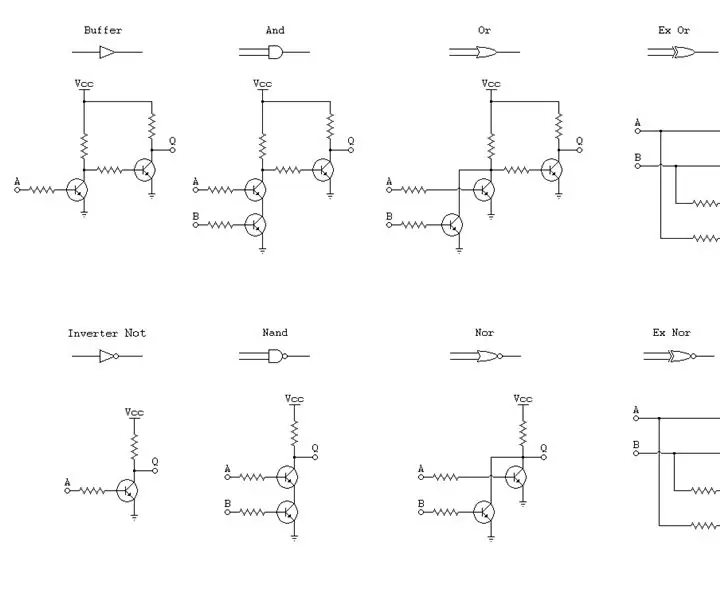

Ik bouw transistorpoorten een beetje anders dan de meeste andere elektronica-ingenieurs. De meeste mensen wanneer ze transistorpoorten bouwen; bouw ze met alleen positieve logica in gedachten, maar poorten in IC's hebben twee logica's, positieve logica en negatieve logica. En ik bouw mijn transistorpoorten met positieve en negatieve logica.

Hoewel er acht poorten zijn; Buffer, Inverter of Not, And, Nand, Or, Nor, Xor en Xnor, ze zijn gemaakt van drie poortcircuits. En wanneer u dubbele logische poorten bouwt, zijn de drie circuits die worden gebruikt om een poort te bouwen Inverter or Not, Nand en Nor, de rest van de poorten zijn gemaakt van twee of meer van deze drie poorten.

Waarom transistorpoorten bouwen? Welnu, hier zijn vijf redenen om uw eigen poorten te bouwen.

1. Je hebt niet de poort die je nodig hebt.

2. U wilt een poort die meer vermogen draagt dan een standaard poort-IC.

3. Je wilt maar één poort en je haat het om de rest van de poorten op de IC te verspillen.

4. Kosten, een omvormer met één transistor is minder dan $ 0,25 en een hex-omvormer-IC is $ 1,00 en hoger.

5. Je wilt poorten beter begrijpen.

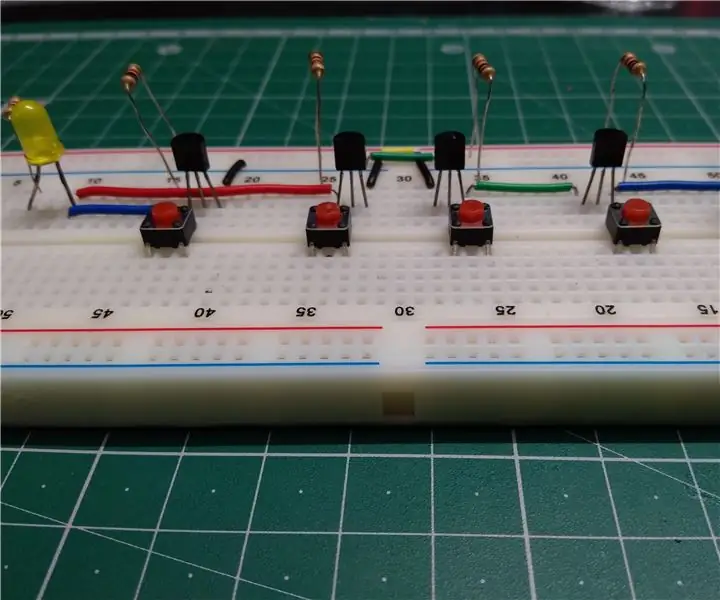

Stap 1: Gereedschap & Onderdelen

De poorten in deze Instructable zijn ¼ watt poorten als je poorten met een hoger wattage wilt bouwen, heb je zwaardere wattage componenten nodig.

Doorverbindingsdraden

Breadboard

Stroomvoorziening

1 x SN74LS04 IC

2 x schakelaars

2 x LED's 1 rood 1 groen

2 x 820 Ω ¼ w weerstanden

2 x 1 kΩ ¼ w weerstanden

3 x 10 kΩ ¼ w weerstanden

3 x NPN-transistors voor algemeen gebruik, ik gebruikte 2N3904.

2 x PNP-transistors voor algemeen gebruik, ik gebruikte 2N3906.

Stap 2: Dubbele logica

Als je de waarheidstabel van een poort opzoekt; zoals een Of-poort met twee ingangen, krijgt u een waarheidstabel die er zo uitziet. Dit is een positieve waarheidstabel voor een Or-poort. Onder A en B is de input naar de gate en Q is de output. 1 staat voor een logische waarde van 1 of + 5 volt en 0 staat voor een logische waarde van 0 of 0 volt. Dus wanneer de meeste mensen een poort bouwen van transistors, bouwen ze een logische waarde van 1 of + 5 volt en een logische waarde van 0 of geen volt. Maar dat is niet wat er gebeurt met de uitgang van een poort, in een IC.

Wanneer de uitgang van een poort van logische waarde 1 naar logische waarde 0 gaat, gaat de uitgang van die poort van + 5 volt met de stroom die uit de uitgang vloeit naar 0 volt met de stroom die naar de uitgang van de poort vloeit. De stroom keert van richting. Wanneer u de omgekeerde stroom gebruikt, wordt dit negatieve logica genoemd, waarbij 0 volt - 1 logische waarde is en + 5 volt - 0 logische waarde is.

Het is het gemakkelijkst om te zien wat dit doet wanneer u de uitgang van een poort aansluit; aan de basis van een NPN-transistor en een PNP-transistor, in serie met een LED. Terwijl de uitgang van de poort logische waarde 1 heeft (5 Volt), is de NPN-transistor gesloten en gaat de LED in serie met de NPN-transistor branden. Wanneer de poortuitgang van logische waarde 1 naar logische waarde 0 gaat (5 volt tot 0 volt), keert de stroom van richting om en opent de NPN-transistor terwijl de PNP-transistor sluit. Hierdoor wordt de LED in serie met de NPN-transistor uitgeschakeld en gaat de LED in serie met de PNP-transistor branden.

Mijn transistorpoorten hebben dezelfde dubbele logica als de poorten in IC's. Terwijl de uitgang van de poort logische waarde 1 heeft (5 Volt), is de NPN-transistor gesloten en gaat de LED in serie met de NPN-transistor branden. Wanneer de poortuitgang van logische waarde 1 naar logische waarde 0 gaat (5 volt tot 0 volt), keert de stroom van richting om en opent de NPN-transistor terwijl de PNP-transistor sluit. Hierdoor wordt de LED in serie met de NPN-transistor uitgeschakeld en gaat de LED in serie met de PNP-transistor branden.

Stap 3: Niet of Inverter Gate

Not of Inverter-poort is de eerste van de 3 poorten die nodig zijn om de andere 5 poorten te maken.

Wanneer de ingang (A) van de inverterpoort 0 of 0 volt is, is de NPN-transistor open en is de uitgang (Q) 1 of +5 volt en gaat eventuele positieve stroom uit de uitgang (Q).

Wanneer de ingang (A) van de inverterpoort 1 of +5 volt is, is de NPN-transistor gesloten en is de uitgang (Q) 0 of 0 volt en gaat elke positieve stroom via de transistor naar aarde.

Stap 4: Nand Gate

De Nand-poort is de tweede van de drie poorten die nodig zijn om de andere 5 poorten te maken.

Wanneer de ingangen (A en B) van de Nand-poort 0 of 0 volt zijn, zijn beide NPN-transistoren open en is de uitgang, (Q) 1 of +5 volt en gaat elke positieve stroom uit de uitgang (Q).

Wanneer de ingang (A) van de Nand-poort 1 of +5 volt is, is de NPN-transistor op A-ingang gesloten. En wanneer de ingang (B) van de Nand-poort 0 of 0 volt is, is de NPN-transistor op B-ingang open en is de uitgang (Q) 1 of +5 volt en gaat elke positieve stroom uit de uitgang (Q).

Wanneer de ingang (A) van de Nand-poort 0 of 0 volt is, is de NPN-transistor op A-ingang open. En wanneer de ingang, (B) van de Nand-poort 1 of +5 volt is, is de NPN-transistor op B-ingang gesloten en de uitgang, (Q) is 1 of +5 volt en elke positieve stroom gaat uit de uitgang (Q).

Wanneer de ingangen (A en B) van de Nand-poort 1 of +5 volt zijn, zijn beide NPN-transistoren gesloten en is de uitgang (Q) 0 of 0 volt en gaat elke positieve stroom via de transistors naar aarde.

Stap 5: Noch Gate

De Nor-poort is de derde van de drie poorten die nodig zijn om de andere 5 poorten te maken.

Wanneer de ingangen (A en B) van de Nor-poort 0 of 0 volt zijn, zijn beide NPN-transistoren open en is de uitgang, (Q) 1 of +5 volt en gaat elke positieve stroom uit de uitgang (Q).

Wanneer de ingang (A) van de Nor-poort 1 of +5 volt is, is de NPN-transistor op A-ingang gesloten. En wanneer de ingang, (B) van de Nor-poort 0 of 0 volt is, is de NPN-transistor op B-ingang open en is de uitgang, (Q) 0 of 0 volt en gaat elke positieve stroom naar aarde via de transistor op A-ingang.

Wanneer de ingang (A) van de Nor-poort 0 of 0 volt is, is de NPN-transistor op A-ingang open. En wanneer de ingang, (B) van de Nor-poort 1 of +5 volt is, is de NPN-transistor op B-ingang gesloten en is de uitgang, (Q) 0 of 0 volt en gaat elke positieve stroom naar aarde via de transistor op B invoer.

Wanneer de ingangen (A en B) van de Nor-poort 1 of +5 volt zijn, zijn beide NPN-transistoren gesloten en is de uitgang (Q) 0 of 0 volt en gaat elke positieve stroom naar aarde via beide transistoren.

Stap 6: Buffer

Een buffer gebruikt twee dezelfde poorten; twee Not- of Inverter-poorten in serie.

Wanneer de ingang (A) van de eerste inverterpoort 0 of 0 volt is, is de NPN-transistor open en is de uitgang 1 of +5 volt naar de ingang van de tweede inverter. Wanneer de ingang van de tweede inverterpoort 1 of +5 volt is, is de NPN-transistor gesloten en is de uitgang (Q) 0 of 0 volt en gaat elke positieve stroom via de transistor naar aarde.

Wanneer de ingang (A) van de eerste inverterpoort 1 of +5 volt is, is de NPN-transistor gesloten en is de uitgang 0 of 0 volt naar de ingang van de tweede inverter. Wanneer de ingang van de tweede inverterpoort 0 of 0 volt is, is de NPN-transistor open en is de uitgang (Q) 1 of +5 volt en gaat elke positieve stroom uit de uitgang (Q).

Stap 7: En Gate

De And-poort is een Nand-poort en een Niet- of Inverter-poort in serie.

De ingangen zijn hetzelfde als de Nand-poort, maar de uitgang wordt omgekeerd door de Niet- of Inverter-poort.

Als de ingangen (A en B) van de And-poort 0 of 0 volt zijn, zijn beide NPN-transistoren open, dan is de uitgang van de eerste poort 1 of +5 volt. Wanneer de ingang van de inverterpoort 1 of +5 volt is, is de NPN-transistor gesloten en is de uitgang (Q) 0 of 0 volt en gaat elke positieve stroom via de transistor naar aarde.

Wanneer de ingang, (A) van de And-poort 1 of +5 volt is, is de NPN-transistor op A-ingang gesloten. En wanneer de ingang, (B) van de And-poort 0 of 0 volt is, is de NPN-transistor op B-ingang open, de uitgang van de eerste poort is 1 of +5 volt. Wanneer de ingang van de inverterpoort 1 of +5 volt is, is de NPN-transistor gesloten en is de uitgang (Q) 0 of 0 volt en gaat elke positieve stroom via de transistor naar aarde.

Wanneer de ingang (A) van de And-poort 0 of 0 volt is, is de NPN-transistor op A-ingang open. En wanneer de ingang, (B) van de And-poort 1 of +5 volt is, is de NPN-transistor op B-ingang gesloten, de uitgang van de eerste poort is 1 of +5 volt. Wanneer de ingang van de inverterpoort 1 of +5 volt is, is de NPN-transistor gesloten en is de uitgang (Q) 0 of 0 volt en gaat elke positieve stroom via de transistor naar aarde.

Wanneer de ingangen (A en B) van de Nand-poort 1 of +5 volt zijn, zijn beide NPN-transistoren gesloten en is de uitgang van de eerste poort 0 of 0 volt. Wanneer de ingang van de inverterpoort 0 of 0 volt is, is de NPN-transistor open en is de uitgang (Q) 1 of +5 volt en gaat elke positieve stroom uit de uitgang (Q).

Stap 8: of poort

De Of-poort is een Nor-poort en een Niet- of Inverter-poort in serie.

De ingangen zijn hetzelfde als de Nor-poort, maar de uitgang wordt omgekeerd door de Niet- of Inverter-poort.

Als de ingangen (A en B) van de Or-poort 0 of 0 volt zijn, zijn beide NPN-transistoren open, dan is de uitgang van de eerste poort 1 of +5 volt. Wanneer de ingang van de inverterpoort 1 of +5 volt is, is de NPN-transistor gesloten en is de uitgang (Q) 0 of 0 volt en gaat elke positieve stroom via de transistor naar aarde.

Wanneer de ingang, (A) van de Or-poort 1 of +5 volt is, is de NPN-transistor op A-ingang gesloten. En wanneer de ingang (B) van de Nor-poort 0 of 0 volt is, is de NPN-transistor op B-ingang open en is de uitgang van de eerste poort 0 of 0 volt. Wanneer de ingang van de inverterpoort 0 of 0 volt is, is de NPN-transistor open en is de uitgang (Q) 1 of +5 volt en gaat elke positieve stroom uit de uitgang (Q).

Wanneer de ingang (A) van de Or-poort 0 of 0 volt is, is de NPN-transistor op A-ingang open. En wanneer de ingang (B) van de Nor-poort 1 of +5 volt is, is de NPN-transistor op B-ingang gesloten en is de uitgang van de eerste poort 0 of 0 volt. Wanneer de ingang van de inverterpoort 0 of 0 volt is, is de NPN-transistor open en is de uitgang (Q) 1 of +5 volt en gaat elke positieve stroom uit de uitgang (Q).

Wanneer de ingangen (A en B) van de Or-poort 1 of +5 volt zijn, zijn beide NPN-transistoren gesloten en is de uitgang van de eerste poort 0 of 0 volt. Wanneer de ingang van de inverterpoort 0 of 0 volt is, is de NPN-transistor open en is de uitgang (Q) 1 of +5 volt en gaat elke positieve stroom uit de uitgang (Q).

Stap 9: Exclusieve Nor Gate (Xnor)

De exclusieve Nor-poort is geconfigureerd als twee Nand-poorten die parallel zijn geschakeld als een Nor-poort met de twee bovenste transistors PNP-transistoren.

Wanneer de ingangen (A en B) van de Xnor-poort 0 of 0 volt zijn, zijn beide NPN-transistoren open en zijn beide PNP-transistoren gesloten. De uitgang (Q) is 1 of +5 volt en elke positieve stroom gaat uit de uitgang (Q).

Wanneer de ingang (A) van de Xnor-poort 1 of +5 volt is, is de NPN-transistor op A-ingang gesloten en is de PNP-transistor open. Als de ingang (B) van de Xnor-poort 0 of 0 volt is, is de PNP-transistor op B-ingang gesloten en is de NPN-transistor open. De uitgang (Q) is 0 of 0 volt en elke positieve stroom gaat naar aarde via de gesloten transistoren.

Wanneer de ingang (A) van de Xnor-poort 0 of 0 volt is, is de NPN-transistor op A-ingang open en is de PNP-transistor gesloten. Als de ingang (B) van de Xnor-poort 1 of +5 volt is, is de PNP-transistor op B-ingang open en is de NPN-transistor gesloten. De uitgang (Q) is 0 of 0 volt en elke positieve stroom gaat naar aarde via de gesloten transistoren.

Als de ingangen (A en B) van de Xnor-poort 1 of +5 volt zijn, zijn de beide NPN-transistoren gesloten en zijn beide PNP-transistoren open. De uitgang (Q) is 1 of +5 volt en elke positieve stroom gaat uit de uitgang (Q).

Stap 10: Exclusief of Gate (Xor)

De Exclusieve Of poort; gebruikt alle drie de belangrijkste poorten, het is geconfigureerd als twee Nand-poorten die parallel zijn geschakeld als een Nor-poort met de twee bovenste transistors PNP-transistoren en een Niet- of Inverter-poort in serie.

De Xor-poortingangen zijn hetzelfde als de Xnor-poort, maar de uitgang wordt omgekeerd door de Niet- of Inverterpoort.

Wanneer de ingangen (A en B) van de Xnor-poort 0 of 0 volt zijn, zijn beide NPN-transistoren open en beide PNP-transistoren gesloten en is de uitgang van de eerste set poorten 1 of +5 volt. Wanneer de ingang van de inverterpoort 1 of +5 volt is, is de NPN-transistor gesloten en is de uitgang (Q) 0 of 0 volt en gaat elke positieve stroom via de transistor naar aarde.

Wanneer de ingang (A) van de Xnor-poort 1 of +5 volt is, is de NPN-transistor op A-ingang gesloten en is de PNP-transistor open. Met de ingang, (B) van de Xnor-poort is 0 of 0 volt, de PNP-transistor op B-ingang is gesloten en de NPN-transistor is open, 0 of 0 volt op de ingang van de omvormer. Wanneer de ingang van de inverterpoort 0 of 0 volt is, is de NPN-transistor open en is de uitgang (Q) 1 of +5 volt en gaat elke positieve stroom uit de uitgang (Q).

Wanneer de ingang (A) van de Xnor-poort 0 of 0 volt is, is de NPN-transistor op A-ingang open en is de PNP-transistor gesloten. Met de ingang (B) van de Xnor-poort is 1 of +5 volt de PNP-transistor op B-ingang is open en de NPN-transistor is gesloten, 0 of 0 volt op de ingang van de omvormer. Wanneer de ingang van de inverterpoort 0 of 0 volt is, is de NPN-transistor open en is de uitgang (Q) 1 of +5 volt en gaat elke positieve stroom uit de uitgang (Q).

Als de ingangen (A en B) van de Xnor-poort 1 of +5 volt zijn, zijn beide NPN-transistoren gesloten en zijn beide PNP-transistoren open. Als de ingang van de tweede Inverter-poort 1 of +5 volt is, is de NPN transistor is gesloten en de uitgang (Q) is 0 of 0 volt en elke positieve stroom gaat via de transistor naar aarde.

Tweede plaats in de Electronics Tips & Tricks Challenge

Aanbevolen:

Logische poorten met transistor: 3 stappen

Logische poorten met transistor: Logische poorten zijn de basisbouwstenen van elk digitaal systeem

Dubbele luidsprekers op hout: 3 stappen

Dubbele luidsprekers op hout: deze Instructable laat je zien wat er gebeurt als je een paar luidsprekers op een stuk hout plaatst. Je kunt het zelf proberen en de veranderingen in de geluidsuitvoer zien. De video laat zien dat de verandering in geluid niet merkbaar is. Echter, speakers op hout zetten

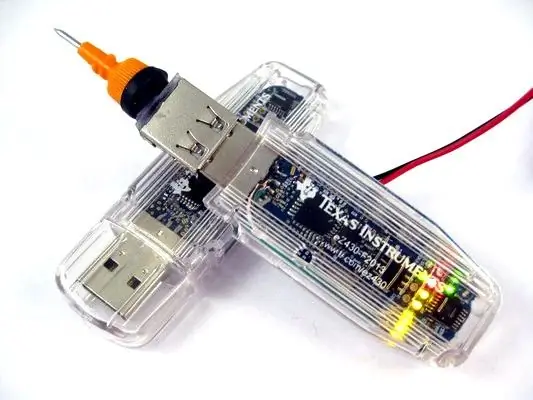

EZProbe, een op EZ430 gebaseerde logische sonde: 4 stappen

EZProbe, een op EZ430 gebaseerde logische sonde: dit is een eenvoudig logische sondeproject gebaseerd op de TI EZ430-dongle. ik heb in september 2010 gebruik gemaakt van een gratis aanbieding op een paar ez430's van TI. ze zijn erg handig en leuk om kleine codefragmenten uit te proberen en de led te zien knipperen. ze hadden sinds b

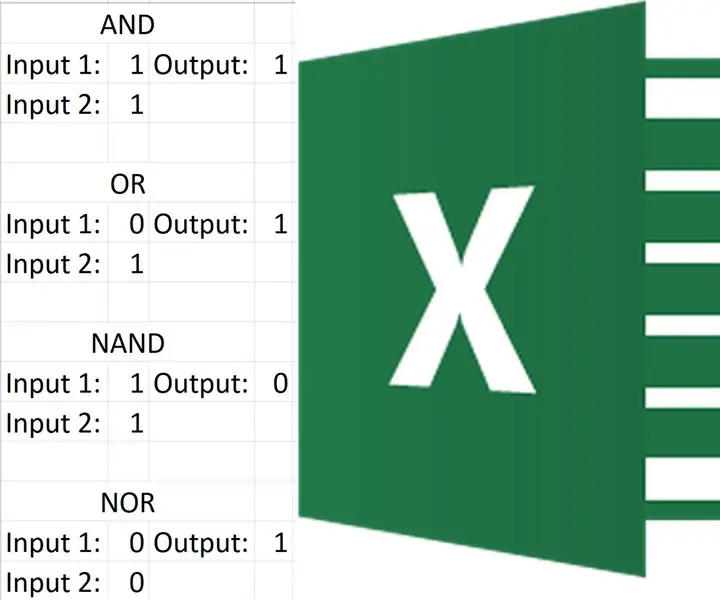

Logische poorten maken in Excel: 11 stappen

Maak logische poorten in Excel: Het maken van alle 7 basis logische poorten in Excel is niet erg moeilijk. Als je de functies in Excel begrijpt, dan zou dit project vrij eenvoudig zijn, als je dat niet doet, geen zorgen, het zal niet lang duren om eraan te wennen. Excel heeft al een paar logische poorten gemaakt voor

Open je ogen! Logische analysator: 21 stappen

Open je ogen! Logische analysator: de logische analysator vergemakkelijkt uw visualisatie van de pulstrein, de bits die in een communicatielijn reizen. Het opent dus je ogen om een mogelijk probleem te identificeren. Waarom is dit belangrijk? Het is een zeer efficiënte ontwikkeling en fout