Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:17.

- Laatst gewijzigd 2025-01-23 15:01.

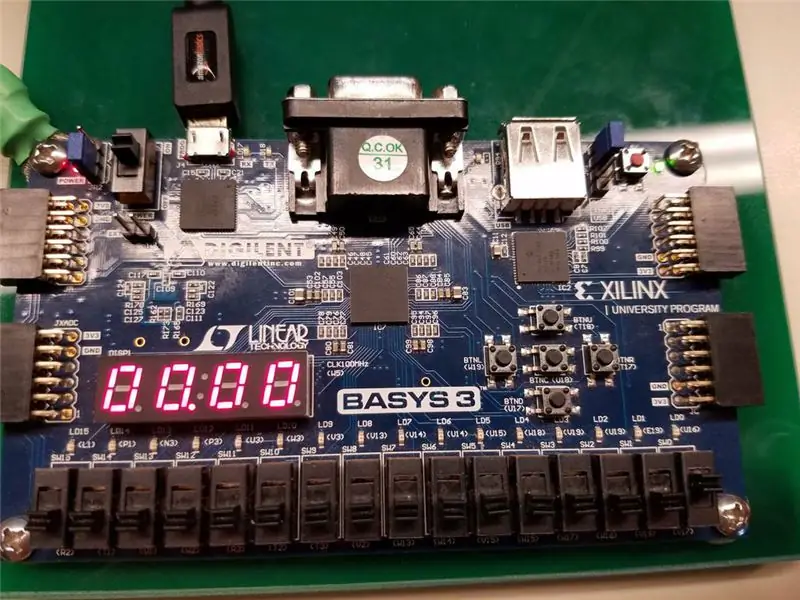

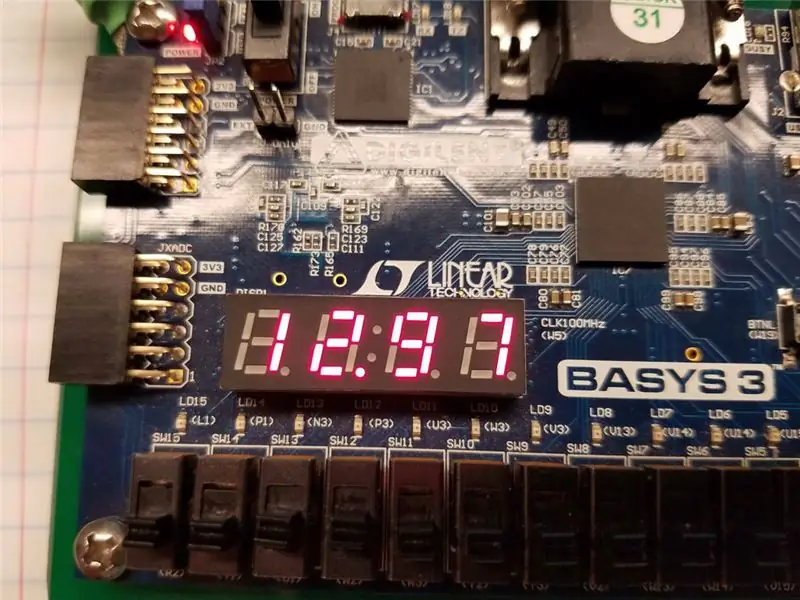

Welkom bij de instructable over het bouwen van een stopwatch met basis VHDL en Basys 3-bord. We zijn verheugd om ons project met u te delen! Dit was een afstudeerproject voor cursus CPE 133 (Digital Design) bij Cal Poly, SLO in de herfst van 2016. Het project dat we hebben gebouwd is een eenvoudige stopwatch die de tijd start, opnieuw instelt en pauzeert. Er zijn drie drukknoppen op het Basys3-bord als invoer nodig en de tijd wordt weergegeven op het viercijferige zevensegmentendisplay van het bord. De verstreken tijd wordt weergegeven in seconden: centiseconden. Het gebruikt de systeemklok van het bord als invoer om de verstreken tijd bij te houden en geeft de tijd door aan de vier cijfers van het zevensegmentendisplay.

Stap 1: Materialen

De materialen die je nodig hebt voor dit project:

- 1 computer met Vivado Design Suite WebPack geïnstalleerd vanaf Xilinx (voorkeur voor versie 2016.2)

- 1 Digilent Basys3 Xilinx Artix-7 FPGA-kaart

- 1 USB-poortkabel

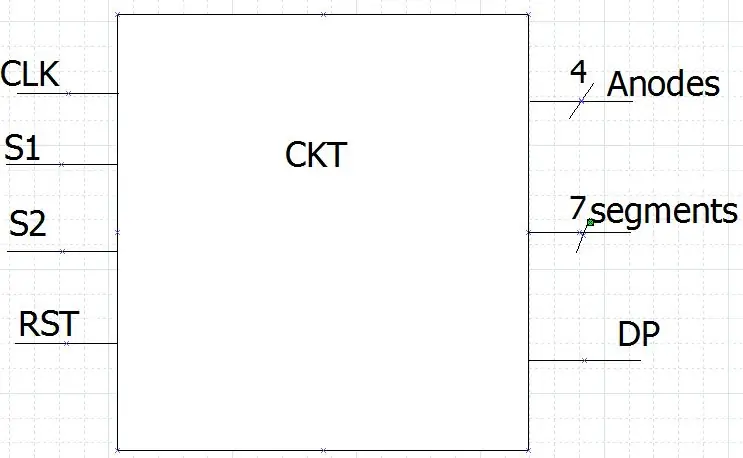

Stap 2: In- en uitgangen instellen

De afbeelding hierboven toont een blokschema op het hoogste niveau van de hoofdstopwatchmodule. De stopwatch heeft ingangen "CLK" (klok), "S1" (startknop), "S2" (pauzeknop) en "RST" (reset) en heeft een 4-bits uitgang "Anodes", een 7-bits output "segment" en een single-bit output "DP" (decimaal punt). Als ingang "S1" hoog is, begint de stopwatch de tijd te tellen. Wanneer "S2" laag is, pauzeert de stopwatch de tijd. Wanneer "RST" hoog is, stopt de stopwatch en stelt de tijd opnieuw in. Er zijn vier submodules in het circuit: de klokverdeler, de cijferteller, de zevensegmentendisplaydriver en de zevensegmentendisplay-encoder. De hoofdmodule van de stopwatch verbindt alle submodules met elkaar en met de in- en uitgangen.

Stap 3: Klokken maken

De klokverdelermodule neemt een systeemklok op en gebruikt een deleringang om een klok te creëren met een snelheid die niet groter is dan die van de systeemklok. De stopwatch gebruikt twee verschillende klokmodules, een die een 500 Hz-klok creëert en een andere die een 100 Hz-klok creëert. Het schema voor de klokverdeler wordt getoond in de bovenstaande afbeelding. De klokdeler neemt een single-bit input "CLK" en een 32-bit input "Divisor" en de single-bit output "CLKOUT" in. "CLK" is de systeemklok en "CLKOUT" is de resulterende klok. De module bevat ook een NOT-poort, die het signaal "CLKTOG" omschakelt wanneer de telling de waarde van de deler bereikt.

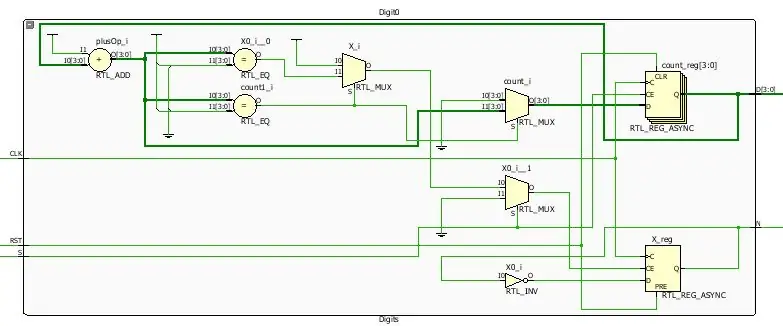

Stap 4: Tellen tot tien

De cijferteller telt elk cijfer van 0 tot 10 en creëert een andere klok voor het volgende cijfer om af te werken van die oscilleert wanneer de telling 10 bereikt. De module neemt 3 enkelbits ingangen "S", "RST" en "CLK in beslag " en resulteert in een enkelbits uitvoer "N" en een 4-bits uitvoer "D". Ingang "S" is de vrijgave in ingang. De klok gaat aan wanneer "S" hoog is en uit wanneer "S" laag is. "RST" is de reset-ingang, dus de klok wordt gereset wanneer "RST" hoog is. "CLK" is de klokingang voor de cijferteller. "N" is de klokuitvoer die de invoerklok wordt voor het volgende cijfer. Uitgang "D" geeft de binaire waarde weer van het cijfer waarop de teller staat.

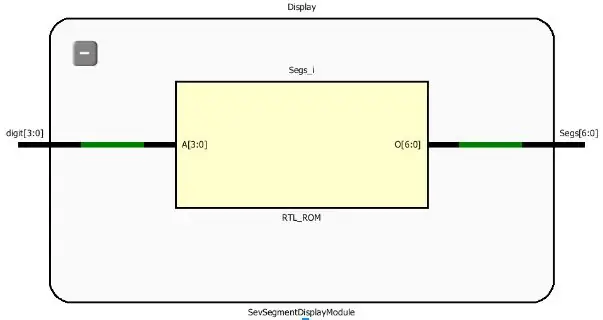

Stap 5: Nummers weergeven

De zeven-segment display-encoder codeert het binaire getal dat wordt ontvangen van de zeven-segment display-stuurprogrammamodule en verandert het in een stroom bits die zal worden geïnterpreteerd als '1'- of '0'-waarden voor elk segment van het display. Het binaire getal wordt door de module ontvangen als de 4-bit invoer "cijfer" en resulteert in de 7-bit uitvoer "segmenten". De module bestaat uit een enkelvoudig procesblok dat een specifieke 7-bits stroom toewijst voor elke mogelijke invoerwaarde van 0 tot 9. Elke bit in de zeven-bits stromen vertegenwoordigt een van de zeven segmenten van de cijfers op het display. De volgorde van de segmenten in de stream is "abcdefg" waarbij '0's de segmenten vertegenwoordigen die oplichten voor het gegeven nummer.

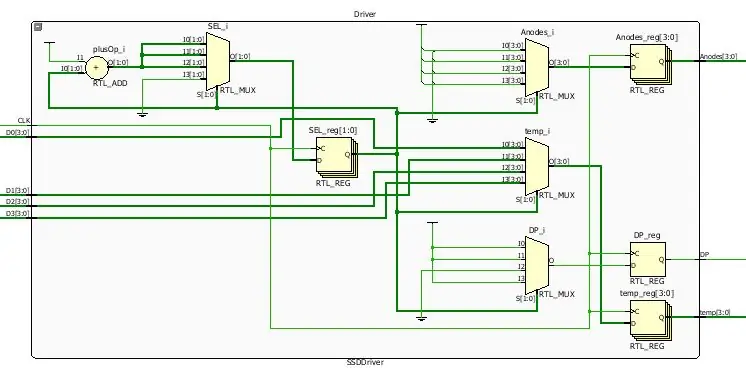

Stap 6: Hoe de stopwatch weer te geven?

In de zeven-segment display driver module zijn er vier 4-bit ingangen "D0", "D1", "D2" en "D3", die elk de vier cijfers vertegenwoordigen die moeten worden weergegeven. Ingang "CLK" is de klokingang van het systeem. Single-bit output "DP" vertegenwoordigt het decimaalteken op het zevensegmentendisplay. De 4-bit uitgang "Anodes" bepaalt welk cijfer op het zeven-segment display wordt weergegeven en de 4-bit uitgang "temp" is afhankelijk van de status van de 2-bit stuuringang "SEL". De module gebruikt 4 multiplexers voor de stuuringang "SEL" en de drie uitgangen; "Anodes", "temp" en "DP".

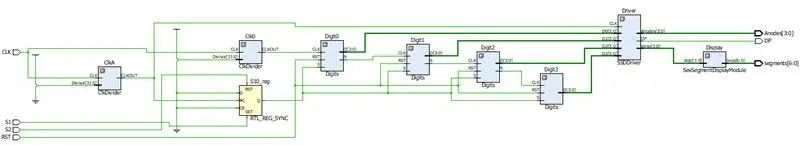

Stap 7: Alles bij elkaar brengen

Een 'if'-procesblok dat van de 500Hz-klok loopt, wordt gebruikt om de start- en pauzeknoppen te maken. Koppel vervolgens alle submodules aan elkaar in de stopwatch-hoofdmodule door de componenten van elke afzonderlijke submodule te declareren en verschillende signalen te gebruiken. De cijfersubmodules nemen de klokuitvoer van de vorige cijfersubmodule op, waarbij de eerste de 100Hz-klok opneemt. De "D"-uitgangen van de cijfersubmodules worden dan de "D"-ingangen van de zevensegmentendisplaydrivermodule. En ten slotte wordt de "temp"-uitgang van de zevensegmentendisplay-stuurprogrammamodule de "temp"-ingang van de zevensegmenten-encodermodule.

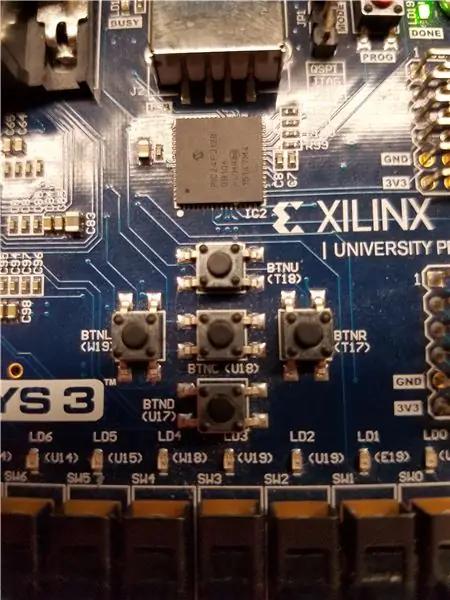

Stap 8: Beperkingen

Gebruik 3 drukknoppen (W19, T17 en U18) voor de ingangen "RST", "S1" en "S2". W19 is de resetknop, T17 is de startknop (S1) en U18 is de pauzeknop (S2). Een beperking voor de klokinvoer is ook vereist bij gebruik van poort W5. Vergeet ook niet om deze regel toe te voegen aan de klokbeperking:

create_clock -add -name sys_clk_pin -periode 10.00 -golfvorm {0 5} [get_ports {CLK}]

Koppel ook de anodes en segmenten aan het bord, zodat de stopwatch wordt weergegeven op het display met zeven segmenten, zoals te zien is in het bestand met beperkingen.

Stap 9: Testen

Zorg ervoor dat je apparaat werkt door met de drie knoppen te spelen: houd ze in elke mogelijke volgorde ingedrukt om eventuele problemen met je code te vinden.

Aanbevolen:

Hoe maak je een stopwatch met Arduino 8 stappen (met afbeeldingen) Antwoorden op al uw "Hoe?"

Hoe maak je een stopwatch met behulp van Arduino: dit is een zeer eenvoudige Arduino 16 * 2 lcd-scherm stopwatch ……….. Als je deze Instructable leuk vindt, abonneer je dan op mijn kanaal https://www.youtube.com /ZenoModiff

Arduino Stopwatch: 4 stappen (met afbeeldingen)

Arduino Stopwatch: deze Instructable laat je zien hoe je een stopwatch maakt van een Arduino

Hoe maak je een digitale stopwatch met behulp van 555: 3 stappen

Hoe maak je een digitale stopwatch met 555: Ik heb een eenvoudige stopwatch gemaakt met behulp van 3 zevensegmenten LED-displays waarvan je eerst voor het weergeven van het 10e deel van seconden een tweede en derde voor een veelvoud van 10 inn seconden. Ik gebruikte 555 timers in de stabiele modus die per 1 seconde signaal geeft aan

Stopwatch voor 30 M hardlopen (Arduino): 6 stappen (met afbeeldingen)

Stopwatch voor 30 M hardlopen (Arduino): Dit project is gemaakt voor een specifiek doel in Finse honkbalcoaching en het testen van de snelheid van juniorspelers in 30 m hardlopen. Dit arduino-project was ook een cursusproject in mijn studie. Het project had wat ups en downs, maar nu is het tenminste werki

VHDL-stopwatch: 8 stappen (met afbeeldingen)

VHDL-stopwatch: dit is een tutorial over het maken van een stopwatch met VHDL en een FPGA-printplaat, zoals een Basys3 Atrix-7-bord. De stopwatch kan tellen van 00.00 seconden tot 99,99 seconden. Het maakt gebruik van twee knoppen, één voor de start/stop-knop en een andere voor de