Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:16.

- Laatst gewijzigd 2025-01-23 15:01.

In deze instructable gaan we een eenvoudige VGA-controller ontwerpen in RTL. VGA-controller is het digitale circuit dat is ontworpen om VGA-schermen aan te sturen. Het leest van Frame Buffer (VGA-geheugen) dat het frame vertegenwoordigt dat moet worden weergegeven, en genereert de nodige gegevens en synchronisatiesignalen voor weergavedoeleinden.

Als u op zoek bent naar Verilog/System verilog-code: Bezoek mijn blog VGA-controller en videosysteem in Verilog

Stap 1: Interface van een VGA-controller

Hieronder volgen de belangrijkste interfacesignalen in een VGA-controller:

- Pixelklok of VGA-klok

- HSYNC- en VSYNC-signalen

Voor het gekozen VGA-scherm moet u eerst de frequentie van de Pixel Clock berekenen die nodig is om het aan te sturen. Het hangt af van 3 parameters: totale horizontale pixels, totale verticale pixels, schermvernieuwingsfrequentie.

Typisch, F = THP * TVP * Verversingsfrequentie

Vind de documentatie over pixelklok die nodig is voor verschillende VGA-schermen in de bijgevoegde RAR.

HSYNC- en VSYNC-signalen worden gegenereerd uit de pixelklok. De timing van HSYNC- en VSYNC-signalen hangt af van een aantal parameters: horizontale en verticale voorporch, horizontale en verticale achterporch, horizontale en verticale weergavepixels, horizontale en verticale synchronisatiepulsbreedtes en polariteiten.

Deze parameters zijn gestandaardiseerd voor een gekozen VGA-scherm. Deze documenten vindt u in de bijgevoegde RAR.

Deze parameters zijn configureerbare parameters in onze VGA Controller IP.

Stap 2: VGA-controller integreren met een VGA-scherm

De afbeelding laat zien hoe u de VGA-controller integreert met een VGA-scherm. U hebt nog twee componenten nodig om het systeem te voltooien:

- Frame Buffer: Geheugen dat het frame bevat dat moet worden weergegeven.

- Video-DAC: DAC die digitale RGB-gegevens omzet en het VGA-scherm aanstuurt met analoge RGB-signalen op het juiste spanningsniveau.

Een van de eenvoudigste en populaire video-DAC's is de ADV7125. Het is een 8-bits DAC die digitale RGB-woorden omzet in analoge signalen van 0-0,7 V en het VGA-scherm aanstuurt.

Stap 3: Framebufferontwerp

Het is het geheugen dat het weer te geven beeld 'opslaat'. Het is meestal een RAM of soms ROM. We zullen bespreken hoe je een framebuffer kunt ontwerpen om een afbeelding weer te geven. Framebuffer geeft deze digitale informatie op commando van VGA-controller door aan een Video DAC.

Eerst moeten we de benodigde pixeldiepte bepalen. Het bepaalt de kwaliteit van de afbeelding, de verscheidenheid aan kleuren die een pixel kan vertegenwoordigen. Voor een 8-bits DAC moeten we de primaire kleurcomponenten van een pixel weergeven: R, G en B in elk 8 bits. Het betekent dat een pixel van 24-bit is.

Elke pixel wordt op een aaneengesloten manier opgeslagen in framebuffergeheugenlocaties.

Stel dat een afbeelding die moet worden weergegeven 800x600 pixels heeft.

Daarom is de benodigde framebuffer 800x600 = 480000 x 24 bits geheugen

Totale grootte van het geheugen is ongeveer 800x600x24 = 1400 kB.

Indien zwart-wit afbeelding, 800x600x1 = 60 kB ong.

Blok-RAM's kunnen worden gebruikt om een framebuffer in Xilinx FPGA's weer te geven.

Stap 4: Opmerkingen

- Afhankelijk van de gekozen DAC zijn extra signalen nodig op de VGA-controller. Ik heb ADV7125 gebruikt.

- Voeg cyclusvertragingen toe via flip-flops op VSYNC en HSYNC voordat u de VGA-weergave aanstuurt. Dit komt door DAC- en geheugenlatenties. De pixelsignalen moeten worden gesynchroniseerd met HSYNC en VSYNC. In mijn geval was het een vertraging van 2 cycli.

- Als framebuffer van een bepaalde grootte niet op FPGA kan worden ontworpen vanwege de beperking van de ram-grootte, gebruik dan kleiner geheugen om de afbeelding weer te geven en bewerk eenvoudig de code om over het adres op de grens van het beschikbare geheugen te rollen, in plaats van over de grens van het volledige frame. Hiermee wordt dezelfde afbeelding steeds opnieuw over het hele scherm gerepliceerd. Een andere methode is pixelschaling waarbij elke pixel wordt gerepliceerd om het hele beeld op volledig scherm weer te geven, in een lagere resolutie. Dit kan worden gedaan door de logica voor adresverhoging in de code aan te passen.

- Het IP is volledig overdraagbaar over alle FPGA's en is timing geverifieerd tot 100 MHz op Virtex-4 FPGA.

Stap 5: Bijgevoegde bestanden

De RAR bevat:

- VGA-controllercode

- PDF's van VGA-standaarden.

Aanbevolen:

Game-saves kopiëren naar een MU van Microsoft of een derde partij op een eenvoudige manier: 9 stappen

Game Saves kopiëren naar een Microsoft of 3rd Party MU op de GEMAKKELIJKE MANIER .: Originele tutorial HIER Er zijn tal van Softmod-tutorials die er zijn en ze zijn allemaal goed, maar het is lastig om de opslagbestanden op de Xbox HDD te krijgen, ik heb een leven gemaakt cd die het eenvoudig maakt om dat te doen. Dit is geen complete softmod-tutorial, dit

Ontwerp van UART in VHDL: 5 stappen

Ontwerp van UART in VHDL: UART staat voor Universal Asynchronous Receiver Transmitter. Het is het meest populaire en eenvoudigste seriële communicatieprotocol. In deze instructable leert u hoe u een UART-module in VHDL ontwerpt

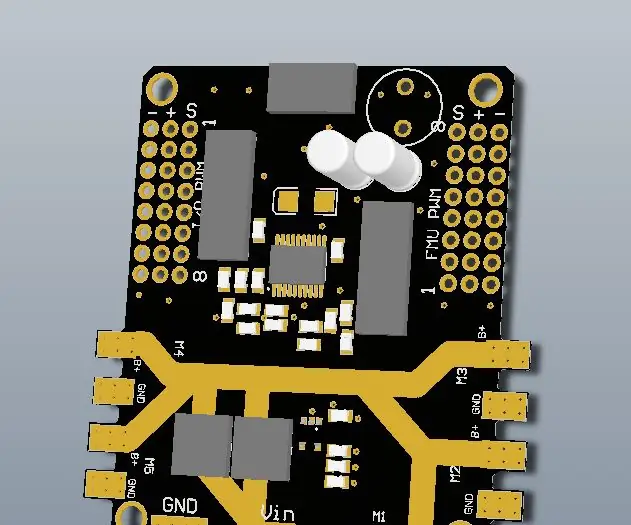

Ontwerp van een High Power PDB (Power Distribution Board) voor een Pixhawk: 5 stappen

Ontwerp van een High Power PDB (Power Distribution Board) voor een Pixhawk: een PCB om ze allemaal van stroom te voorzien! Momenteel zijn de meeste materialen die je nodig hebt om een drone te bouwen goedkoop verkrijgbaar op internet, dus het idee om een zelfontwikkelde PCB te maken is het helemaal niet waard, behalve een paar gevallen waarin je een rare en

Een batterijpakket van 4,5 volt maken van een batterij van 9 V: 4 stappen

Een 4,5 volt batterijpakket maken van een 9V-batterij: deze instructie gaat helemaal over het splitsen van een 9V-batterij in 2 kleinere 4,5V-batterijpakketten. De belangrijkste reden om dit te doen is 1. Je wilt 4,5 volt 2. Je wilt fysiek iets kleiners dan een 9V batterij

Instructies voor het voltooien van de mock-up van het ontwerp van de rupsschuif voor het heffen/verlagen van in het midden gemonteerde voetsteunen op elektrische rolstoelen - Ajarn

Instructies voor het voltooien van de mock-up van het ontwerp van de rupsschuif voor het omhoog/omlaag brengen van in het midden gemonteerde voetsteunen op elektrische rolstoelen: in het midden gemonteerde voetsteunen kunnen omhoog worden gebracht om onder de zitting goed te worden opgeborgen en omlaag om te worden ingezet. Een mechanisme voor onafhankelijke bediening van het opbergen en plaatsen van de voetsteun is niet inbegrepen in elektrische rolstoelen op de markt, en PWC-gebruikers hebben de behoefte geuit