Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:16.

- Laatst gewijzigd 2025-01-23 15:01.

In mijn vorige instructable zagen we hoe we een eenvoudige direct toegewezen cachecontroller kunnen ontwerpen. Deze keer gaan we een stap verder. We gaan een eenvoudige associatieve cachecontroller met vier standen ontwerpen. Voordeel ? Minder fouten, maar ten koste van de prestaties. Net als mijn vorige blog, zouden we een volledige processor, hoofdgeheugen en cache-omgeving ontwerpen en emuleren om onze cachecontroller te testen. Ik hoop dat jullie dit een nuttige referentie vinden om de concepten te begrijpen en in de toekomst je eigen cachecontrollers te ontwerpen. Aangezien het model voor de processor (testbank) en het hoofdgeheugensysteem exact hetzelfde zijn als mijn vorige blog, zal ik ze niet nogmaals uitleggen. Raadpleeg de vorige instructable voor meer informatie hierover.

Stap 1: Specificaties:

Bekijk snel de specificaties van de Cache Controller die hier wordt gepresenteerd:

- Four-way Set Associative Cache Controller (ga naar deze link als u op zoek bent naar Direct Mapped Cache Controller).

- Single-Banked, blokkerende cache.

- Doorschrijfbeleid voor schrijfhits.

- Write-Around-beleid voor schrijffouten.

- Tree Pseudo-LRU (pLRU) Vervangingsbeleid.

- Tag Array binnen de controller.

- Configureerbare parameters.

Standaardspecificaties voor cachegeheugen en hoofdgeheugen zijn hetzelfde als in mijn vorige instructable. Raadpleeg ze.

Stap 2: RTL-weergave van het hele systeem

De volledige RTL-weergave van de Top Module is weergegeven in de afbeelding (exclusief de processor). Standaardspecificaties voor de bussen zijn:

- Alle databussen zijn 32-bits bussen.

- Adresbus = 32-bits bus (maar slechts 10 bits zijn hier adresseerbaar door het geheugen).

- Datablok = 128 bits (Wide Bandwidth Bus for Read).

- Alle componenten worden aangedreven door dezelfde klok.

Stap 3: Testresultaten

De Top Module is getest met behulp van een testbank, die eenvoudig een niet-gepipelinede processor modelleert, net zoals we deden in de laatste instructable. De testbank genereert regelmatig lees-/schrijfgegevensverzoeken naar het geheugen. Dit bespot typische "Load" en "Store" instructies, gebruikelijk in alle programma's die door een processor worden uitgevoerd.

De testresultaten hebben de functionaliteit van de Cache Controller met succes geverifieerd. Hieronder volgen de waargenomen teststatistieken:

- Alle Read/Write Miss- en Hit-signalen zijn correct gegenereerd.

- Alle bewerkingen voor het lezen/schrijven van gegevens waren op alle vier de manieren succesvol.

- pLRU-algoritme is met succes geverifieerd voor de vervanging van cacheregels.

- Geen problemen met incoherentie/inconsistentie van gegevens gedetecteerd.

- Het ontwerp is met succes gecontroleerd op timing voor een Maxm. Klokfrequentie van werking = 100 MHz in Xilinx Virtex-4 ML-403 Board (hele systeem), 110 MHz voor alleen cachecontroller.

- Blok-RAM's werden afgeleid voor het hoofdgeheugen. Alle andere arrays zijn geïmplementeerd op LUT's.

Stap 4: Bijgevoegde bestanden

De volgende bestanden zijn hier bij deze blog bijgevoegd:

- . VHD-bestanden van Cache Controller, Cache Data Array, Main Memory System.

- Testbank.

- Documentatie op Cache Controller.

Opmerkingen:

- Ga door de documentatie voor een volledig begrip van de specificaties van de Cache Controller die hier wordt gepresenteerd.

- Alle wijzigingen in de code zijn afhankelijk van andere modules. De veranderingen moeten dus oordeelkundig worden gedaan.

- Besteed aandacht aan alle opmerkingen en headers die ik heb gegeven.

- Als om welke reden dan ook blok-RAM's niet worden afgeleid voor het hoofdgeheugen, VERMINDER dan de grootte van het geheugen, gevolgd door wijzigingen in de adresbusbreedtes over de bestanden, enzovoort. Zodat hetzelfde geheugen kan worden geïmplementeerd op LUT's of gedistribueerd RAM. Dit bespaart de routeringstijd en middelen. Of ga naar de specifieke FPGA-documentatie en zoek de compatibele code voor Block RAM en bewerk de code dienovereenkomstig, en gebruik dezelfde adresbusbreedtespecificaties. Dezelfde techniek voor Altera FPGA's.

Aanbevolen:

Game-saves kopiëren naar een MU van Microsoft of een derde partij op een eenvoudige manier: 9 stappen

Game Saves kopiëren naar een Microsoft of 3rd Party MU op de GEMAKKELIJKE MANIER .: Originele tutorial HIER Er zijn tal van Softmod-tutorials die er zijn en ze zijn allemaal goed, maar het is lastig om de opslagbestanden op de Xbox HDD te krijgen, ik heb een leven gemaakt cd die het eenvoudig maakt om dat te doen. Dit is geen complete softmod-tutorial, dit

Ontwerp van UART in VHDL: 5 stappen

Ontwerp van UART in VHDL: UART staat voor Universal Asynchronous Receiver Transmitter. Het is het meest populaire en eenvoudigste seriële communicatieprotocol. In deze instructable leert u hoe u een UART-module in VHDL ontwerpt

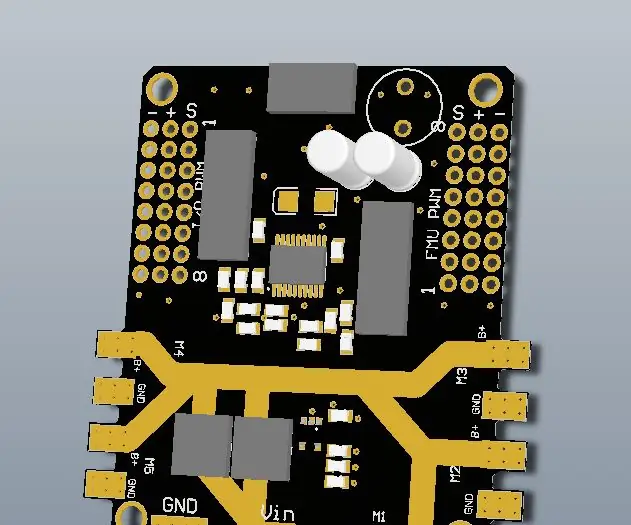

Ontwerp van een High Power PDB (Power Distribution Board) voor een Pixhawk: 5 stappen

Ontwerp van een High Power PDB (Power Distribution Board) voor een Pixhawk: een PCB om ze allemaal van stroom te voorzien! Momenteel zijn de meeste materialen die je nodig hebt om een drone te bouwen goedkoop verkrijgbaar op internet, dus het idee om een zelfontwikkelde PCB te maken is het helemaal niet waard, behalve een paar gevallen waarin je een rare en

Een batterijpakket van 4,5 volt maken van een batterij van 9 V: 4 stappen

Een 4,5 volt batterijpakket maken van een 9V-batterij: deze instructie gaat helemaal over het splitsen van een 9V-batterij in 2 kleinere 4,5V-batterijpakketten. De belangrijkste reden om dit te doen is 1. Je wilt 4,5 volt 2. Je wilt fysiek iets kleiners dan een 9V batterij

Instructies voor het voltooien van de mock-up van het ontwerp van de rupsschuif voor het heffen/verlagen van in het midden gemonteerde voetsteunen op elektrische rolstoelen - Ajarn

Instructies voor het voltooien van de mock-up van het ontwerp van de rupsschuif voor het omhoog/omlaag brengen van in het midden gemonteerde voetsteunen op elektrische rolstoelen: in het midden gemonteerde voetsteunen kunnen omhoog worden gebracht om onder de zitting goed te worden opgeborgen en omlaag om te worden ingezet. Een mechanisme voor onafhankelijke bediening van het opbergen en plaatsen van de voetsteun is niet inbegrepen in elektrische rolstoelen op de markt, en PWC-gebruikers hebben de behoefte geuit