Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:14.

- Laatst gewijzigd 2025-01-23 15:01.

JDM is een populaire PIC-programmeur omdat het een seriële poort gebruikt, een absoluut minimum aan componenten en geen voeding nodig heeft. Maar er is verwarring daarbuiten, met veel programmeervariaties op het net, welke werken met welke PIC's? In deze "instructable" hebben we JDM op de proef gesteld en ik demonstreer hoe je het circuit kunt simuleren met Spice, dat al je vragen zal beantwoorden!

Benodigdheden

LTspice die hier kan worden gedownload van Analog Devices.

Je hebt hier ook de JDM-circuitbestanden nodig.

Stap 1: Vereisten voor seriële poorten

JDM vereist een seriële poort die voldoet aan de EIA232-specificatie, idealiter met +12/-12 spanningsniveaus.

Volgens Texas Instruments Line Driver MC1488 datasheet (Figuur 3)

Uitgangsimpedantie = 4V/8mA = 500 ohm.

Kortsluitstroomlimiet =12mV, zonder tijdslimiet - geen schade aan de chip.

Ingangsimpedantie van lijnontvanger = 3k tot 7k ohm aanbevolen.

Seriële poorten op oudere desktop-pc's gebruiken +12v/-12V om aan deze vereiste te voldoen.

Seriële poorten op nieuwere laptops gebruiken lagere spanningen. JDM kan wel of niet werken - het antwoord is complexer.

Stap 2: Vereisten voor PIC-programmering

Informatie over PIC-programmeringsvereisten wordt verkregen van Microchip. Het bovenstaande is voor een typisch apparaat.

Stap 3: JDM-specificatie:

Is de originele JDM-website verloren gegaan in de nevelen van de tijd? Dit laat ons raden wat de ontwerper oorspronkelijk bedoelde met de specificatie.

- Bieden VDD=5V, en tot IDD=2mA maximum (voor “in socket” versie)

- Verstrek VHH=13V, en tot maximaal IHH=0.2mA.

- MCLR Stijgtijd tVHHR = 1uS max.

- ICSP-versie moet MCLR laag kunnen trekken tegen 22k pull-up op doel.

Stap 4: Circuitbeschrijving:

Afbeelding JDM1 is gebaseerd op het "standaard" JDM-circuit van de PICPgm-website. Dit is de "PIC in Socket"-programmeur waarbij PIC stroom krijgt van TX- en RTS-pinnen. Het oorspronkelijke diagram was moeilijk te begrijpen, dus ik heb het opnieuw getekend met de normale conventie van stroom van boven naar beneden. En ik heb LED-indicatoren "RESET", "PROG" en "RTS" toegevoegd die nodig zijn tijdens constructie en testen. Hopelijk hebben deze geen nadelig effect op het gedrag.

De normale conventie van circuitontwerp is om alle gronden te gemeen hebben, maar het belangrijkste kenmerk van JDM is dat seriële poortaarde (GND) is verbonden met VDD. Dit zorgt voor verwarring omdat seriële poortsignalen worden gemeten met betrekking tot GND, PIC-signalen met betrekking tot logische aarde (VSS).

Wanneer TX hoog wordt, gedraagt Q1 zich als twee voorwaarts voorgespannen diodes. (Q1-collector is niet omgekeerd voorgespannen zoals bij normale transistorwerking). Q1-collector laadt C2, die is geklemd op VDD+8V door Zener (D3). Q1-emitter levert 13V aan MCLR voor programma-/verificatiemodus.

Wanneer TX laag wordt, wordt condensator C3 opgeladen via D1 en wordt VSS geklemd op VDD-5V door zener (D5). Ook TX wordt vastgeklemd op (VSS-0.6) door D1. Q1 is uit, C1 houdt zijn lading vast voor de volgende programmeerpuls. MCLR is geklemd op 0V door D2, dus de PIC is nu Reset.

Wanneer RTS hoog is, wordt de klok verzonden naar PGC. D4 klem PGC op VDD logic high. Wanneer RTS laag is, wordt condensator C3 opgeladen via D6 en wordt VSS geklemd op VDD-5V door zener (D5). D6 klemt PGC op VSS of logisch 0.

Tijdens het programmeren worden gegevens die op DTR worden verzonden, gelezen op PGD, die de PIC als invoer configureert. Wanneer DTR hoog is, fungeert Q2 als "emittervolger" en is de PGD-spanning ongeveer (VDD-0.6) of logisch 1. Wanneer DTR laag is, werkt Q2 als een slechte transistor (emitter- en collectorpinnen omgekeerd). Q2 trekt PGD laag, die wordt vastgeklemd door D7 op VSS of logische 0.

Tijdens de verificatie configureert de PIC PGD als een uitgang voor het verzenden van gegevens naar de seriële poort. DTR moet hoog zijn ingesteld en gegevens worden gelezen op CTS. Wanneer de PGD-uitgang hoog is, is Q2 uit, CTS = DTR = +12V. Als de PGD-uitgang laag is, is Q2 aan. Q2-collector trekt stroom (12V+5V)/(1k+1k5)=7mA van DTR en trekt CTS laag naar VSS.

Stap 5: Bereid je voor op simulatie

Download LT spice, bewaar en open de circuitbestanden (*.asc) die hier worden verstrekt. Om het circuit te simuleren, moeten we het een aantal inputs geven en vervolgens de outputs "traceren". V1, V2 V3 simuleert de 12V seriële poort met uitgangsimpedantie R11, R12, R13.

- V1 genereert 2 programmapulsen op TX van 0,5 ms tot 4,5 ms

- V2 genereert burst van datapulsen op DTR van 1,5 tot 4,5 ms

- V3 genereert burst van klokpulsen op RTS van 0,5 tot 3,5 ms

De componenten V4, X1, R15 en R16 maken allemaal deel uit van de simulatie.

- V4 genereert 2 pulsen van 2,5 tot 4,5 ms voor verificatiegegevens.

- Jumper X1 simuleert OUTPUT op PGD.

- R15, R16 simuleren het "laden" van PIC op VDD en MCLR.

Stap 6: Aanpassingen voor ICSP

Figuur JDM3 toont de versie voor “in circuit” programmering. Wijzigingen van het origineel zijn:

- Vervang de ZIF-socket door een ICSP-connector.

- De PIC wordt nu gevoed door voeding naar het doelcircuit (V5).

- Verwijder de 5V zener (D5).

- De kleine 100pF condensator (C4) wordt naast de PIC op het doelcircuit geplaatst.

- LED's nemen waar mogelijk stroom van de printplaat.

- De MCLR pull-up weerstand (R10) en diode (D10) zijn vereist op het doelcircuit.

- WAARSCHUWING. Het doelbord moet een "zwevende" voeding hebben, idealiter een batterij.

- Sluit de doelaarde (VSS) niet aan op de computer/pc-aarde door tegelijkertijd met JDM andere computerpoorten aan te sluiten.

Na het simuleren van JDM1 werd het probleem van de lange oplaadtijd op C2 duidelijk. Dan blijkt na het lezen van Fruttenboel dat C2 en Q1 als modificatie aan het origineel zijn toegevoegd. Ik kan niet bedenken wat C2 en Q1 zijn bedoeld om te doen, afgezien van het creëren van problemen. Dus voor JDM4 keren we terug naar het oudere ontwerp op Fruttenboel, dat eenvoudig en duidelijk te begrijpen is. D1 en D3/LED2 klem MCLR tussen VSS en VDD+8V. De waarde van R1 is teruggebracht tot 3k3, net voldoende om LED2 op 12V te verlichten.

JDM4 is ook ontworpen om te werken met zwakkere seriële poorten. Wanneer TX hoog wordt (+9V), TX-stroombron = (9-8)/(1k +3k3) = 0.2ma, net genoeg om MCLR hoog te trekken, hoewel onvoldoende om LED2 te verlichten. Wanneer TX laag wordt (ongeveer -7V), TX-stroomafvoer = (9-7)/1k = 2mA. LED1 stroom = (7-2 voor led)/(2k7) = 1.8mA. MCLR pull-down stroom = 7-5,5/3k3 = 0,5mA.

Dit circuit is ook getest (JDM5-simulatie) om te zien wat er gebeurt met seriële poorten +/-7V minimum, waar er onvoldoende spanning is om VHH=13V te ondersteunen. Het doel van C1 wordt nu duidelijk, C1 creëert een korte +ve boost naar MCLR, een 33us piek op de stijgende flank van TX, lang genoeg om de PIC in de programmeermodus te laten komen, misschien? Maar verwijder jumper X2 (deactiveer LED1) omdat er onvoldoende stroom is om MCLR laag te trekken en LED1 samen te verlichten. Wanneer TX laag wordt, is TX stroomafvoer = (7V-5,5V)/(1k+3k3) = 0,3mA, net voldoende om MCLR laag te trekken tegen de pull-up R10.

Stap 7: Simulatieresultaten

Om de grafische bestanden te bekijken, is het beter om met de rechtermuisknop op de onderstaande links te klikken en vervolgens "Link openen in nieuw tabblad" te selecteren

Simulatie 1: spoor van MCLR, VSS en RTS voor originele JDM1. Meteen zijn waarneming 1, 2 en 3 duidelijk.

Simulatie 2: spoor van MCLR en VSS, en RTS voor gewijzigde JDM2, die eerdere problemen oplost.

Simulatie 3: spoor van PGD, VSS en PGC voor JDM2 verzenden van gegevens in programmamodus. Observatie 4 bij 3,5 mS.

Simulatie 4: spoor van PGD, VSS en CTS voor JDM2 in verificatiemodus (jumper X1 geplaatst). Oke

Simulatie 5: spoor van MCLR, VSS, PGD en PGC voor JDM3. ICSP met behulp van stroom uit het circuit lost veel problemen op.

Simulatie 6: spoor van MCLR, VSS, PGD en PGC voor JDM4 met +/-9V seriële poort. MCLR stijgt onmiddellijk, volledig werkend.

Simulatie 7: spoor van MCLR, VSS en TX voor JDM5 met +/- 7V seriële poort en jumper X2 verwijderd. C1 creëert een +ve boost (piek) op de stijgende rand van MCLR, ongeveer voldoende om MCLR boven TX naar 13V te duwen.

Stap 8: Conclusies

Spice is echt goed in het onthullen van "verborgen geheimen" van de werking van circuits. Het is duidelijk dat het JDM-circuit werkt en compatibel is met veel PIC-chips, maar de volgende observaties onthullen mogelijke beperkingen/compatibiliteitsproblemen/fouten?

- Lange stijgtijd van MCLR terwijl C2 oplaadt naar VPP bij de eerste puls van TX. Voldoet niet aan specificatie 3.

- De seriële poort laadt C2 op wanneer TX hoog wordt en RTS laag. Maar RTS heeft ook de taak om C3 op te laden. Wanneer beide tegelijkertijd optreden, creëert dit meer belasting op RTS, bijgevolg verliest C3 lading (VSS stijgt) bij 2 ms bij simulatie. Gebrek aan specificatie 1.

- C3 verliest lading (VSS begint te stijgen) nadat klokpulsen stoppen bij 3,5 ms.

- Wat is het doel van C2, het is überhaupt nodig?

Oplossingen

- Vermoedelijk gebruikt PICPgm een software "work-round". Het moet een lange TX-puls geven om voor te laden naar C2, en dan pas naar de programmeermodus gaan na de tweede TX-puls? Voor simulatie heb ik de waarde van C2 verlaagd tot 1uF om een stijgtijd van 1ms te geven. Geen ideale oplossing.

- Splits C2 en C3 zodat ze onafhankelijk van elkaar worden opgeladen. Een kleine wijziging aan JDM2, C2 verwijst naar GND in plaats van VSS.

- Opgelost door JDM3. ICSP is veel betrouwbaarder omdat PIC wordt aangedreven door een doelcircuit.

- JDM4 lost probleem 1 op. Dit is een eenvoudig ontwerp waarbij C2 helemaal wordt geëlimineerd.

Stap 9: En tot slot

Het bewijs van de pudding zit in het eten. Deze JDM werkt dus blijf hem gebruiken.

En mijn aanbevelingen zijn:

- gebruik JDM2 voor in socket programmering en 12V seriële poorten,

- gebruik JDM4 voor ICSP-programmeur en seriële poorten boven +/- 9V,

- gebruik JDM4 met jumper X2 verwijderd voor seriële poorten boven +/-7V.

Referenties:

Analog Devices LT spice

picpgm

Fruttenboel

Volg meer PIC-projecten op sly-corner

Aanbevolen:

Elegoo Super Started Kit Uno R3 Review: 4 stappen

Elegoo Super Started Kit Uno R3 Review: Een paar dagen geleden stuurde Elegoo me deze Super Starter Kit om te testen. Laten we dus eens kijken wat erin zit. Bij het openen van deze compacte behuizing kunnen we veel dingen zien. Op de omslag staat een index met alle onderdelen. Binnenin hebben we een bedankkaart met alle s

Hoe ESP8266 AT Firmware te flashen of programmeren met behulp van ESP8266 Flasher en Programmer, IOT Wifi-module - Ajarnpa

Hoe ESP8266 AT-firmware te flashen of programmeren met behulp van ESP8266 Flasher en Programmer, IOT Wifi-module: Beschrijving: Deze module is een USB-adapter / programmeur voor ESP8266-modules van het type ESP-01 of ESP-01S. Het is handig uitgerust met een 2x4P 2,54 mm vrouwelijke header om de ESP01 aan te sluiten. Ook breekt het alle pinnen van de ESP-01 uit via een 2x4P 2,54 mm mannelijke h

(bijna) Universal MIDI SysEx CC Programmer (en Sequencer): 7 stappen (met afbeeldingen)

(bijna) Universal MIDI SysEx CC Programmer (en Sequencer…): Halverwege de jaren tachtig begonnen synths-fabrikanten een "less is better" proces dat leidde tot barebones-synths. Dit zorgde voor een verlaging van de kosten aan de kant van de fabrikant, maar maakte het patchproces vervelend, zo niet onmogelijk voor het uiteindelijke gebruik

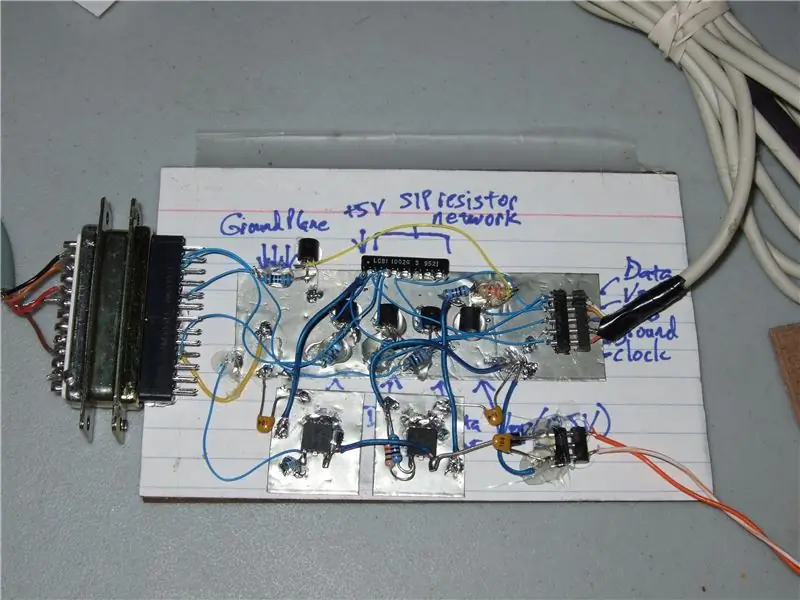

5 Transistor PIC Programmer * Schematisch toegevoegd aan stap 9!: 9 stappen

5 Transistor PIC Programmer *Schema toegevoegd aan Stap 9!: Maak uw eigen PIC programmer voor de parallelle poort van uw computer. Dit is een variatie op het klassieke ontwerp van David Tait. Het is zeer betrouwbaar en er is gratis goede programmeersoftware beschikbaar. Ik hou van IC-Prog en PICpgm programmeur. Het beste van alles is dat het

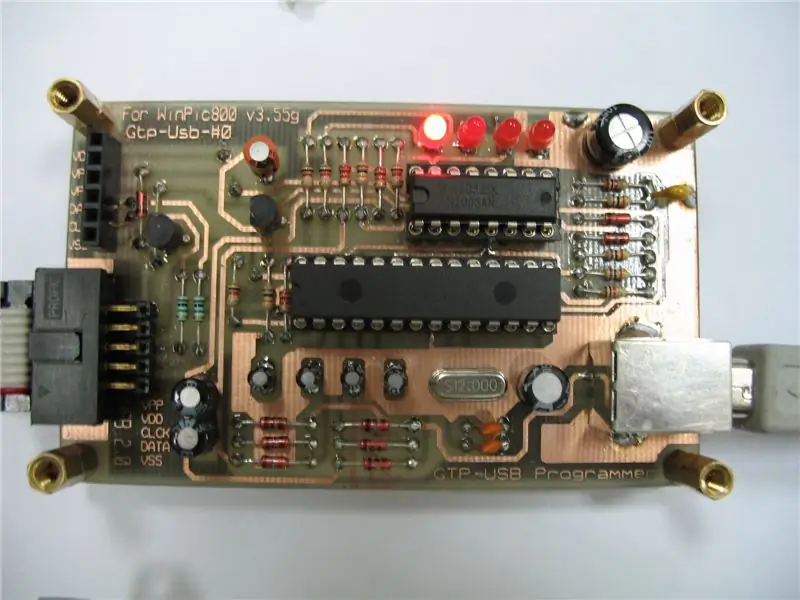

GTP USB PIC PROGRAMMER (Open Source): 5 stappen (met afbeeldingen)

GTP USB PIC PROGRAMMER (Open Source): Dit werk omvat GTP USB (niet plus of lite). Het schema, de foto's en de PCB zijn ontwikkeld door PICMASTERS op basis van een aantal waardevolle werken die eerder zijn gedaan. Deze programmeur ondersteunt pic10F, 12F, 16C, 16F, 18F, 24Cxx Eeprom. Helaas, het w