Inhoudsopgave:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 11:14.

- Laatst gewijzigd 2025-01-23 15:01.

In deze tutorial gaan we de FPGA gebruiken om het externe LED-circuit te besturen. We gaan de volgende taken uitvoeren:

(A) Gebruik de drukknoppen op FPGA Cyclone IV DuePrologic om de LED te bedienen.

(B) Flash-LED periodiek aan en uit

Videodemo

Labmenu:

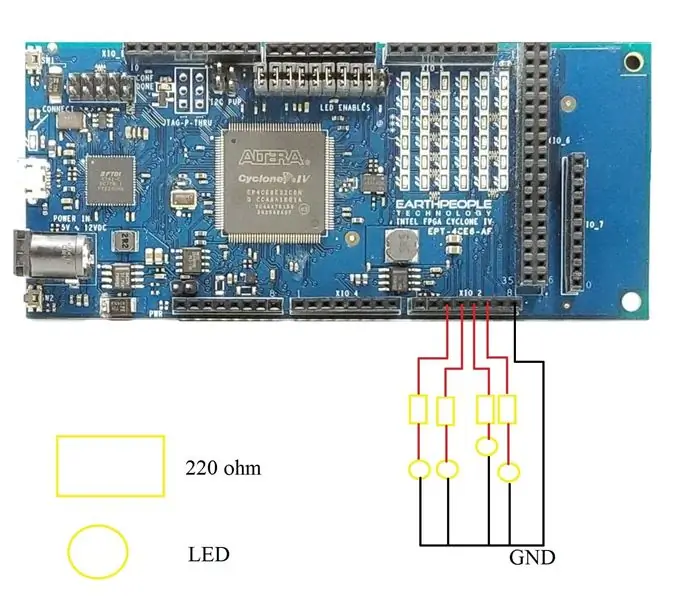

Stap 1: Bouw een elektronisch circuit

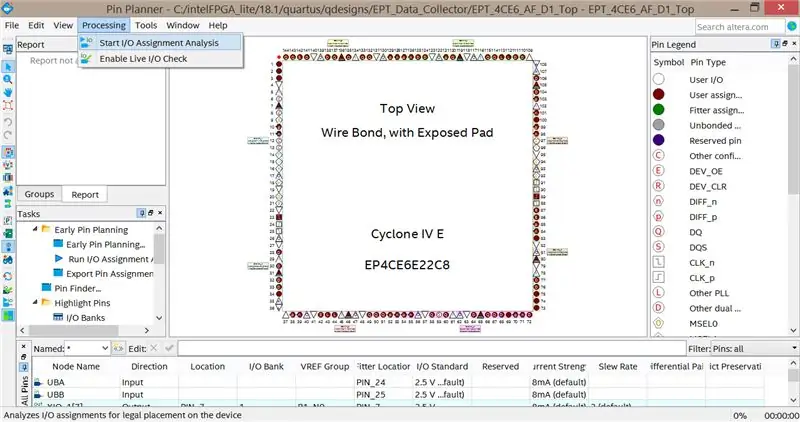

Stap 2: Controleer de Pin Planner en bewerk de Verilog-code

Stap 3: Verilog-code bewerken

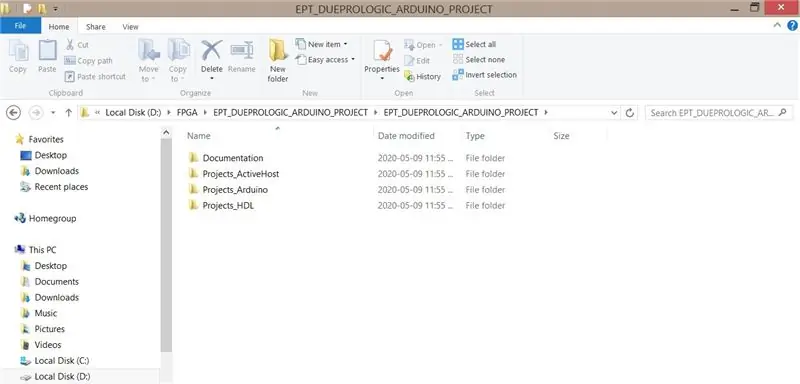

Wanneer u FPGA DueProLogic koopt, zou u een dvd moeten ontvangen. Nadat je "Projects_HDL" hebt geopend, zou je het originele codebestand moeten zien

Voeg de gemarkeerde code toe. Het registreert de I/O-poorten en wijst nummers toe aan de poorten.

uitgangsdraad [7:0] XIO_1, //XIO -- D2-D9

uitgangsdraad [5:0] XIO_2, //XIO -- D10-D12

uitgangsdraad [5:0] XIO_3, //XIO -- D22-D29

ingangsdraad [5:0] XIO_4, //XIO -- D30-D37

ingangsdraad [5:0] XIO_5, //XIO -- D38-D45

uitgangsdraad [4:0] XIO_6_OUT, //XIO -- D46-D53

ingangsdraad [31:5] XIO_6, //XIO -- D46-D53

uitgangsdraad [2:0] XIO_7, //XIO -- D69, D70, D71, D74, D75, D76

ingangsdraad UBA, // Drukknopschakelaars

ingangsdraad UBB // Drukknopschakelaars

toewijzen XIO_1[3] = start_stop_cntrl;

toewijzen XIO_2[1] = start_blinky; // LED-flitser LED aan en uit

toewijzen XIO_2[2] = 1'b1; //uitvoer HOOG

toewijzen XIO_2[3] = ~UBA; //Drukknop A

toewijzen XIO_2[4] = UBB; //Drukknop B

wijs c_enable = XIO_5[2] toe;

wijs LEDExt = XIO_5[5] toe;

Dan moeten we een vertragingstimer instellen. Geef commentaar op de originele timercode en schrijf een nieuwe timerfunctie

//-----------------------------------------------

// LED Knipperende start

//-----------------------------------------------

/*

altijd @(posedge CLK_66 of negedge RST)

beginnen

als(!RST)

start_blinky <= 1'b0;

anders

beginnen

if(control_register[7:4] > 0)

start_blinky <= 1'b1;

anders

start_blinky <= 1'b0;

einde

einde

*/

reg [31:0] ex;

eerste begin

ex <= 32'b0;

start_blinky <= 1'b0;

einde

altijd @(posedge CLK_66)

beginnen

ex <= ex + 1'b1;

if (ex > 100000000) // flits aan/uit ~ 1,6 seconden, klok 66 MHz

beginnen

start_blinky <= !start_blinky;

ex <= 32'b0;

einde

einde

//-----------------------------------------------

// LED-vertragingstimerteller

//-----------------------------------------------

/*

altijd @(posedge CLK_66 of negedge RST)

beginnen

als(!RST)

led_delay_counter <= TIMER_LOW_LIMIT;

anders

beginnen

if(staat[SELECT_MODE])

led_delay_counter <= timer_value;

else if(staat[WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

einde

einde*/

Stap 4: Verilog-code compileren

Druk op "Start Compilatie" in Quartus, er mag geen foutmelding worden gegenereerd.

Als u een foutmelding krijgt over meerdere pinnen. Ga naar Assignments -> Device -> Device and Pin Options -> Dual-Purpose Pins -> verander de waarde van de juiste pin in "Use as regular I/O".

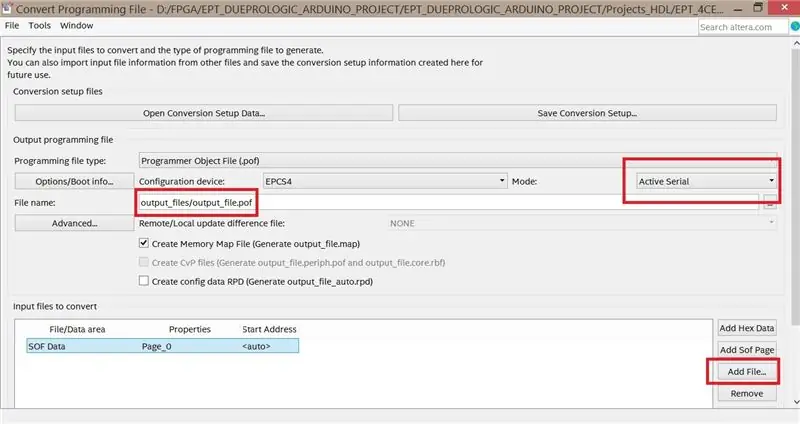

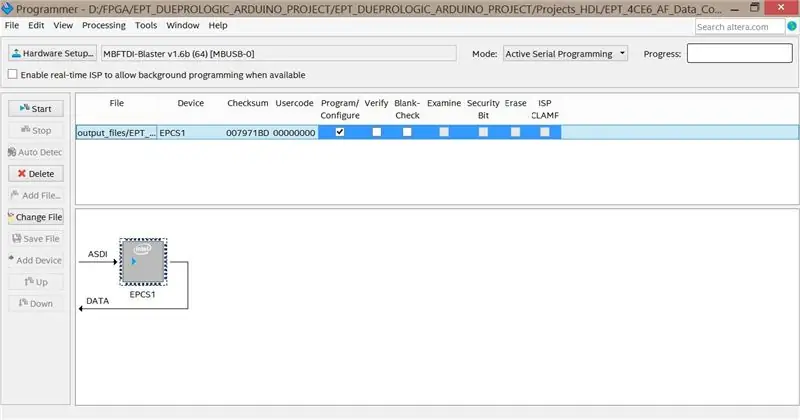

Na de compilatie zou u het pof-uitvoerbestand rechtstreeks moeten krijgen. Als uw software niet up-to-date is, krijgt u mogelijk alleen een soft-bestand. Wanneer dit gebeurt, klikt u op "Bestand" in Quartus -> "programmeerbestanden converteren". Wijzig de instellingen die zijn gemarkeerd door rode vakjes.

Stap 5: Laten we het proberen

Het moet tenslotte lukken!!! De gele LED is altijd aan. De rode LED knippert. De blauwe LED gaat uit als u op knop B drukt. De groene LED gaat aan als u op knop A. drukt

Aanbevolen:

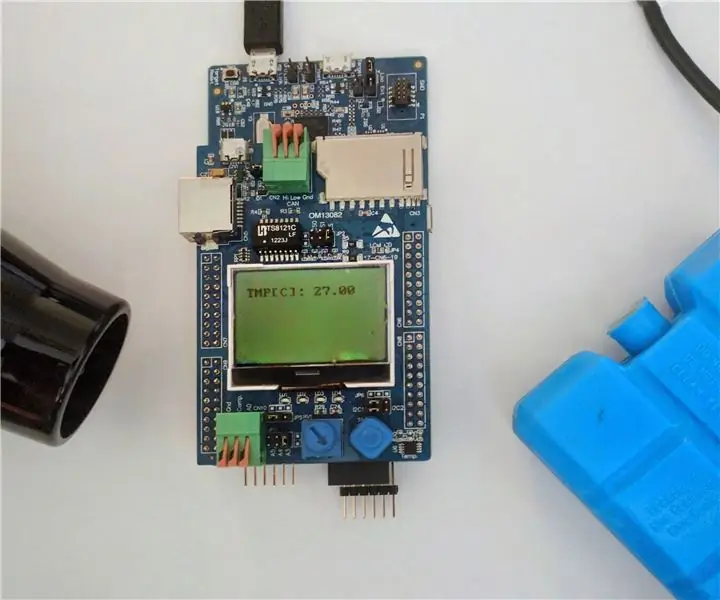

Maak elke sensor uit een FPGA: 4 stappen

Maak elke sensor uit een FPGA: de meeste makers hebben minstens één keer in hun leven geprobeerd een thermometer te bouwen, misschien is degene die ze thuis hebben niet slim genoeg, of misschien denken ze dat ze het volgende NEST kunnen bouwen. Niettemin hadden ze op een gegeven moment een microcontroller met hun status

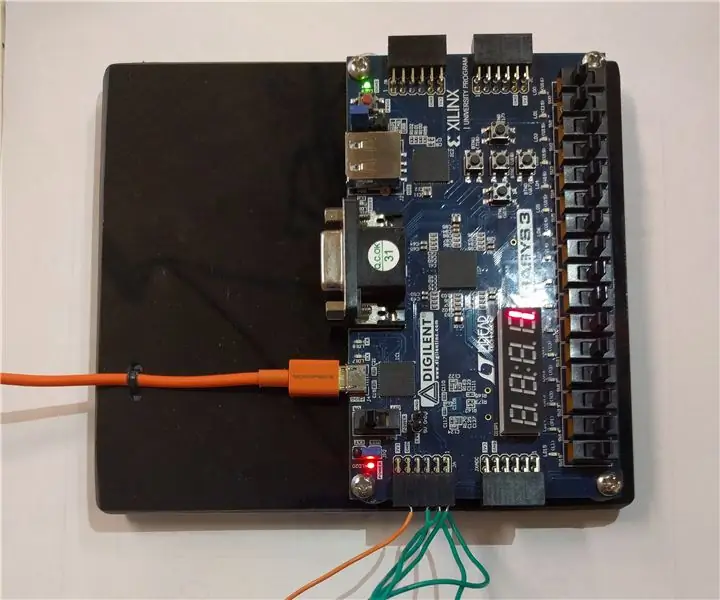

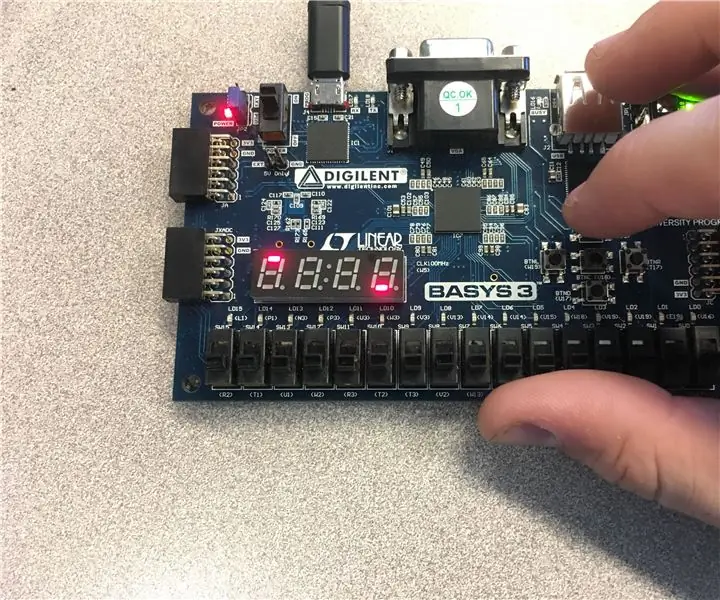

FPGA-reactiespel: 10 stappen

FPGA-reactiespel: tegen de zomer Rutherford en Regita Soetandar

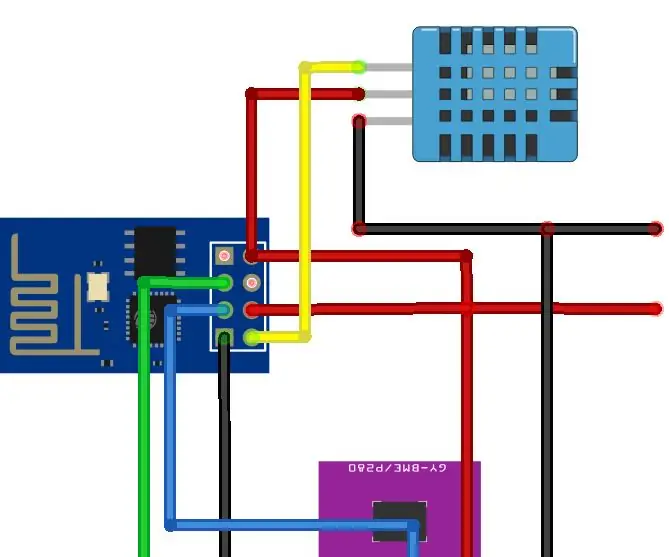

Nog een Arduino-weerstation (ESP-01 & BMP280 & DHT11 & OneWire): 4 stappen

Nog een Arduino-weerstation (ESP-01 & BMP280 & DHT11 & OneWire): hier vindt u een iteratie van het gebruik van OneWire met de weinige pinnen van een ESP-01. Het apparaat dat in deze instructable is gemaakt, maakt verbinding met het wifi-netwerk van uw keuze (u moet de inloggegevens hebben…) Verzamelt sensorische gegevens van een BMP280 en een DHT11

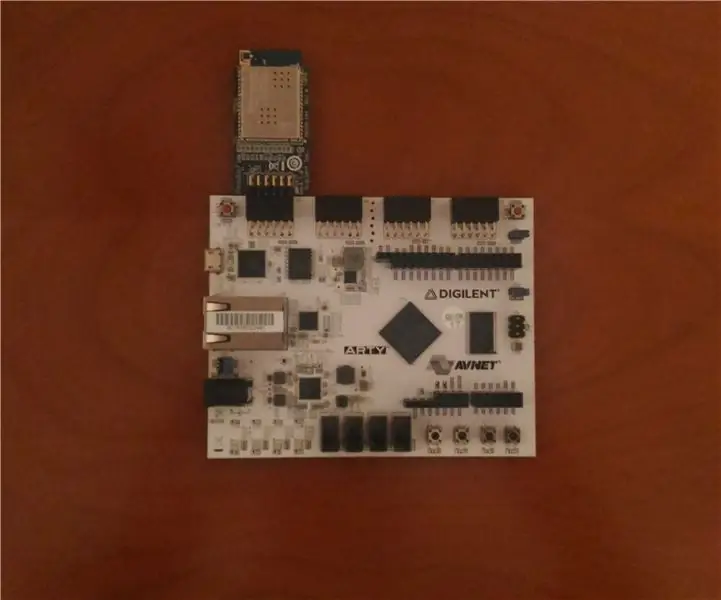

PmodWiFi FPGA-stuurprogramma: 9 stappen

PmodWiFi FPGA-stuurprogramma: dit is een Instructable voor diegenen die een Pmod WiFi willen gebruiken in combinatie met een FPGA-bord

FPGA Asteroid Game: 7 stappen (met afbeeldingen)

FPGA Asteroid Game: Voor ons CPE 133 Final Project hebben we besloten om een asteroïden-game te maken op onze FPGA met behulp van twee drukknopschakelaars en het 7-segments display. De game werkt zo dat een asteroïde spawnt in een van de drie willekeurig geselecteerde rijen en naar de